32

CHAPTER 2 CPU

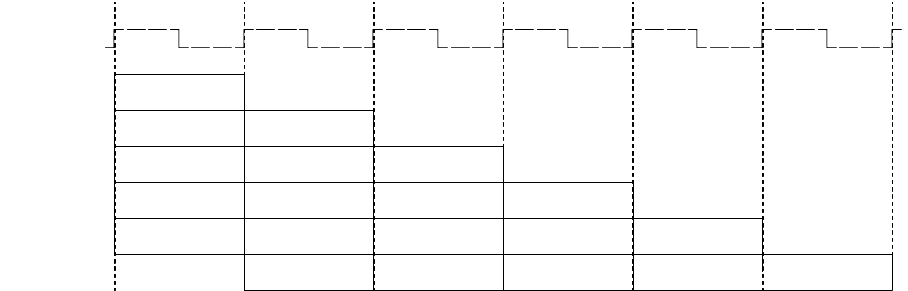

Figure 2.2-2 Instruction Pipeline

Instructions are always executed in order. That is, instruction A that is put into the pipeline

before instruction B always reaches the write back stage before instruction B.

Instructions are normally executed at a rate of one instruction per cycle. However, a load/store

instruction involving memory wait, branch instruction without a delay slot, or multiple-cycle

instruction, requires multiple cycles to complete execution. The instruction execution speed is

also slowed down when instruction supply takes time.

❍

"32 bits <--> 16 bits" bus converter

The "32 bits <--> 16 bits" bus converter interfaces between the D-BUS that allows high-speed

32-bit wide access and R-BUS that allows 16-bit wide access. It thus enables the CPU to

access data in the internal peripheral circuits.

Upon receipt of a 32-bit wide access from the CPU, the bus converter converts it into two 16-bit

wide accesses to implement access to the R-BUS. Some internal peripheral circuits have

restrictions on access width.

❍

"Harvard <--> Princeton" bus converter

The "Harvard <--> Princeton" bus converter coordinates the instruction access and data access

of the CPU to implement smooth interfacing with the external bus.

The CPU has Harvard architecture in which the instruction bus and data bus are independent of

each other. The bus controller that controls the external bus has Princeton architecture

consisting of a single bus. The bus converter gives priority to the instruction and data accesses

of the CPU to control accesses to the bus controller. This control always optimizes the order of

access to the external bus.

The bus converter has a two-word write buffer to eliminate the CPU’s bus wait time and a one-

word prefetch buffer for instruction fetch.

Instruction 1

Instruction 2

Instruction 3

Instruction 4

Instruction 5

Instruction 6

CLK

WB

WB

WB

WB

WB

MA

MA

MA

MA

MA WB

EX

EX

EX

EX

ID

ID

ID

IF

IF