204

CHAPTER 5 I/O PORTS

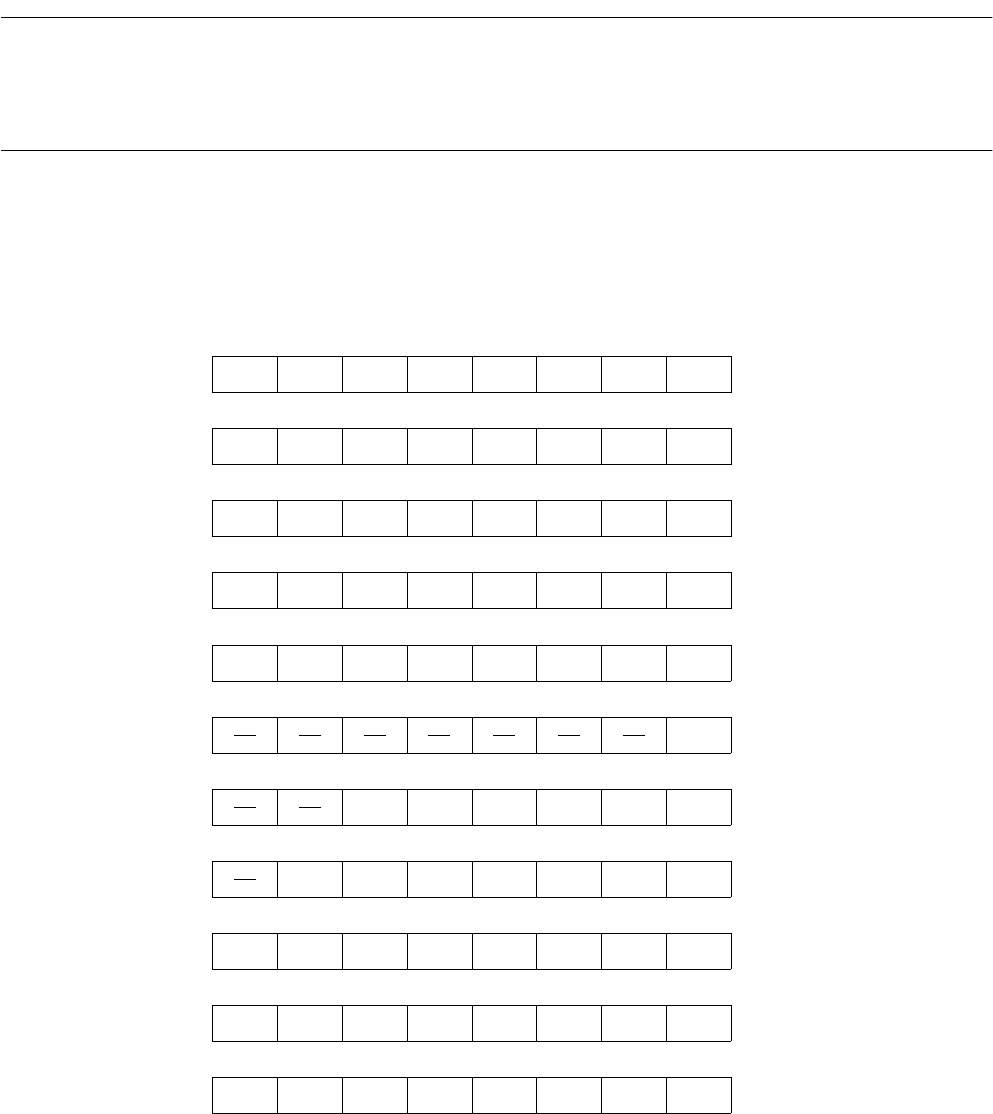

5.3 Data Direction Register (DDR)

The data direction registers (DDR2 to DDRF) control the I/O direction of the

corresponding I/O ports in bit units.

Set 0 to perform input control, and set 1 to perform output control.

■

Configuration of Data Direction Register (DDR)

The data direction register (DDR) is configured as follows:

7654 3210

DDR2

Address: 000601

H

P27 P26 P25 P24 P23 P22 P21 P20 00000000

B

W

7654 3210

DDR3

Address: 000600

H

P37 P36 P35 P34 P33 P32 P31 P30 00000000

B

W

7654 3210

DDR4

Address: 000607

H

P47 P46 P45 P44 P43 P42 P41 P40 00000000

B

W

7654 3210

DDR5

Address: 000606

H

P57 P56 P55 P54 P53 P52 P51 P50 00000000

B

W

7654 3210

DDR6

Address: 000605

H

P67 P66 P65 P64 P63 P62 P61 P60 00000000

B

W

7654 3210

DDR7

Address: 000604

H

P70 -------0

B

W

7654 3210

DDR8

Address: 00060B

H

P85 P84 P83 P82 P81 P80 --000000

B

W

7654 3210

DDRA

Address: 000609

H

PA6 PA5 PA4 PA3 PA2 PA1 PA0 -0000000

B

W

7654 3210

DDRB

Address: 000608

H

PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 00000000

B

W

7654 3210

DDRE

Address: 0000D2

H

PE7 PE6 PE5 PE4 PE3 PE2 PE1 PE0 00000000

B

W

7654 3210

DDRF

Address: 0000D3

H

PF7 PF6 PF5 PF4 PF3 PF2 PF1 PF0 00000000

B

W

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access

Initial value

Access