414

APPENDIX E Instructions

■

Memory Store Instructions

*: Special register Rs: TBR, RP, USP, SSP, MDH, MDL

(Notes)

The assembler calculates and sets values in the o8 and o4 fields of hardware specifications as

follows:

Disp10/4 --> o8, disp9/2 --> o8, disp8 --> o8: Disp10, disp9, and disp8 are signed.

Udisp6/4 --> o4: Udisp6 is unsigned.

■

Interregister Transfer Instructions

*: Special register Rs: TBR, RP, USP, SSP, MDH, MDL

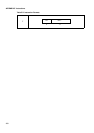

Table E.1-9 Memory Store Instructions

Mnemonic Type OP Cycle NZVC Operation Remarks

ST Ri, @Rj

ST Ri, @(R13,Rj)

ST Ri, @(R14,disp10)

ST Ri, @(R15,udisp6)

ST Ri, @-R15

ST Rs, @-R15

ST PS, @-R15

A

A

B

C

E

E

E

14

10

30

13

17-0

17-8

17-9

a

a

a

a

a

a

a

----

----

----

----

----

----

----

Ri-->(Rj)

Ri-->(R13 + Rj)

Ri-->(R14 + disp10)

Ri-->(R15 + udisp6)

R15 - = 4,Ri-->(R15)

R15 - = 4,Rs-->(R15)

R15- = 4,PS-->(R15)

Word

Word

Word

Rs: Special register*

STH Ri, @Rj

STH Ri, @(R13,Rj)

STH Ri, @(R14,disp9)

A

A

B

15

11

50

a

a

a

----

----

----

Ri-->(Rj)

Ri-->(R13+Rj)

Ri-->(R14+disp9)

Half-word

Half-word

Half-word

STB Ri, @Rj

STB Ri, @(R13,Rj)

STB Ri, @(R14,disp8)

A

A

B

16

12

70

a

a

a

----

----

----

Ri-->(Rj)

Ri-->(R13+Rj)

Ri-->(R14+disp8)

Byte

Byte

Byte

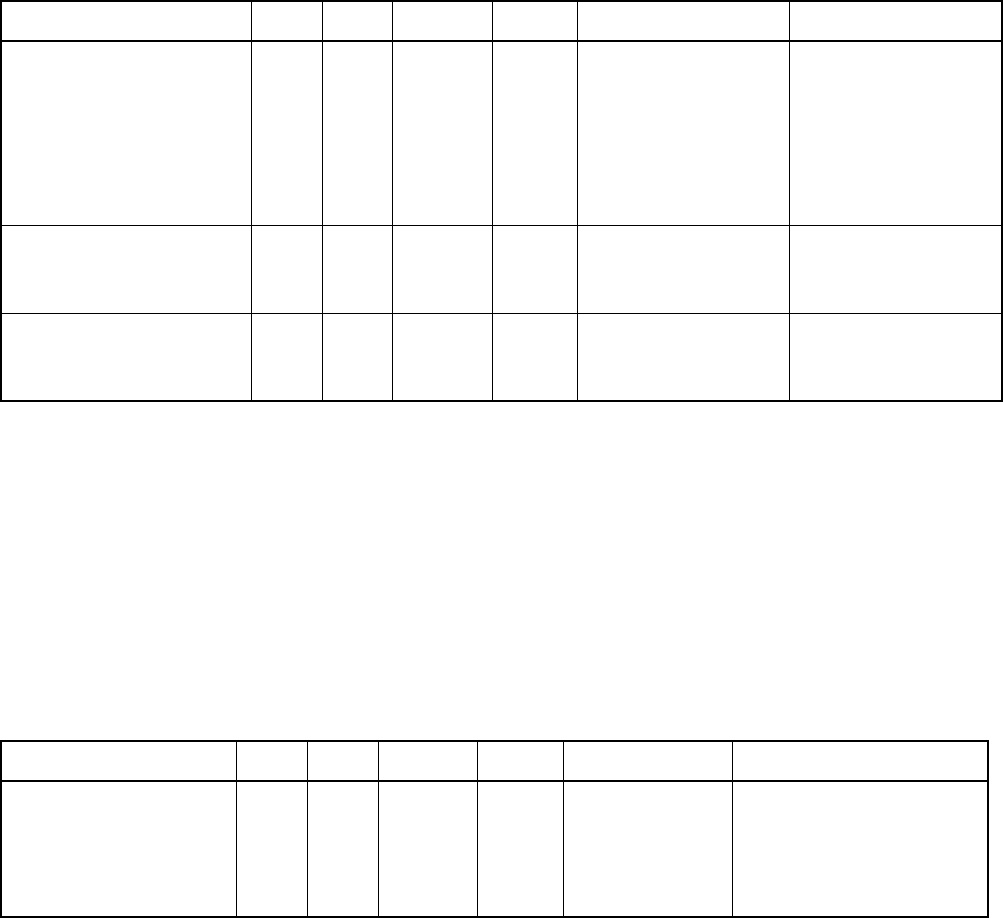

Table E.1-10 Interregister Transfer Instructions

Mnemonic Type OP Cycle NZVC Operation Remarks

MOV Rj, Ri

MOV Rs, Ri

MOV Ri, Rs

MOV PS, Ri

MOV Ri, PS

A

A

A

E

E

8B

B7

B3

17-1

07-1

1

1

1

1

c

----

----

----

----

CCCC

Rj --> Ri

Rs --> Ri

Ri --> Rs

PS --> Ri

Ri --> PS

Transfer between

general-purpose registers

Rs: special register*

Rs: special register*