39

2.3 Programming Model

2.3.3 Program Status Register (PS)

The program status register holds the program status in three parts, ILM, SCR, and

CCR. The undefined bits are all reserved. When the register is read, 0 is always read

from these bits.

No data can be written to this register.

■

Program Status Register (PS)

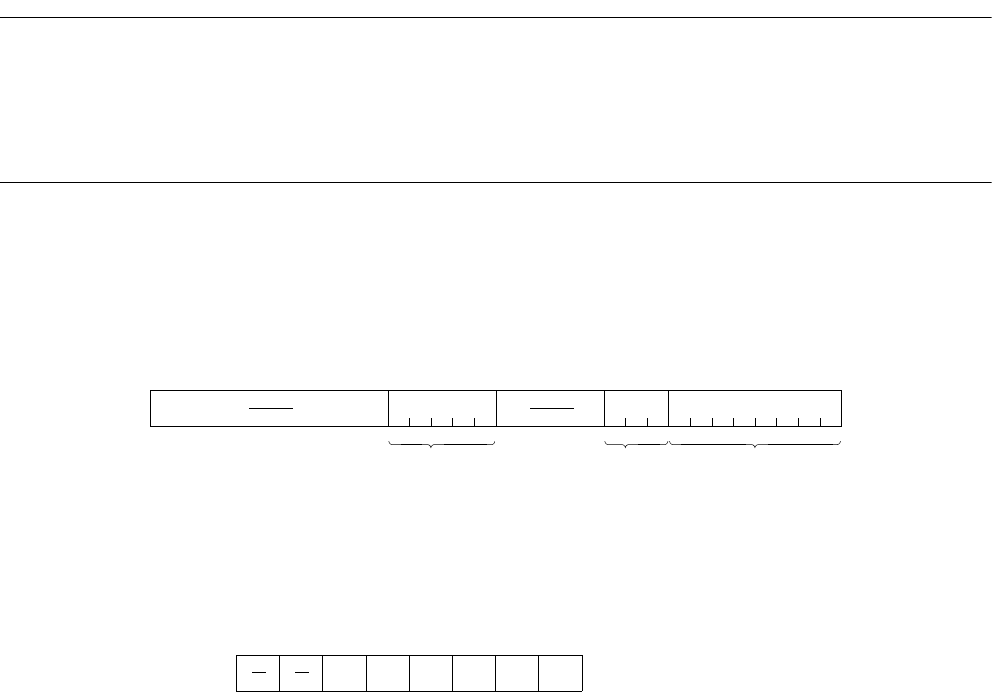

The configuration of the program status register (PS) is shown below:

❍

Condition code register (CCR)

The configuration of the condition code register (CCR) is shown below:

[bit 5] S: Stack flag

This bit specifies the stack pointer used as R15.

0: Uses SSP as R15.

The bit is automatically set to 0 when EIT occurs.

1: Uses USP as R15.

This bit is cleared to 0 by resetting.

Set the bit to 0 when the RETI instruction is executed.

[bit 4] I: Interrupt enable flag

This bit enables or disables a user interrupt request.

0: Disables user interrupts.

The bit is cleared to 0 when the INT instruction is executed.

(The value before the bit is cleared is saved to the stack.)

1: Enables user interrupts.

The masking of user interrupt requests is controlled by the value held in the ILM.

This bit is cleared to 0 by resetting.

31 20 16 10 8 7 0

ILM SCR CCR

--00XXXX

B

S

INZ

VC

[Initial value]

7

65

43

2

10