284

CHAPTER 12 16-BIT RELOAD TIMER

12.2 Control Status Register (TMCSR)

The control status register is used to control the 16-bit timer operation mode and

interrupts.

Set the bits other than UF, CNTE, and TRG again when CNTE is 0.

Simultaneous writing is enabled.

■

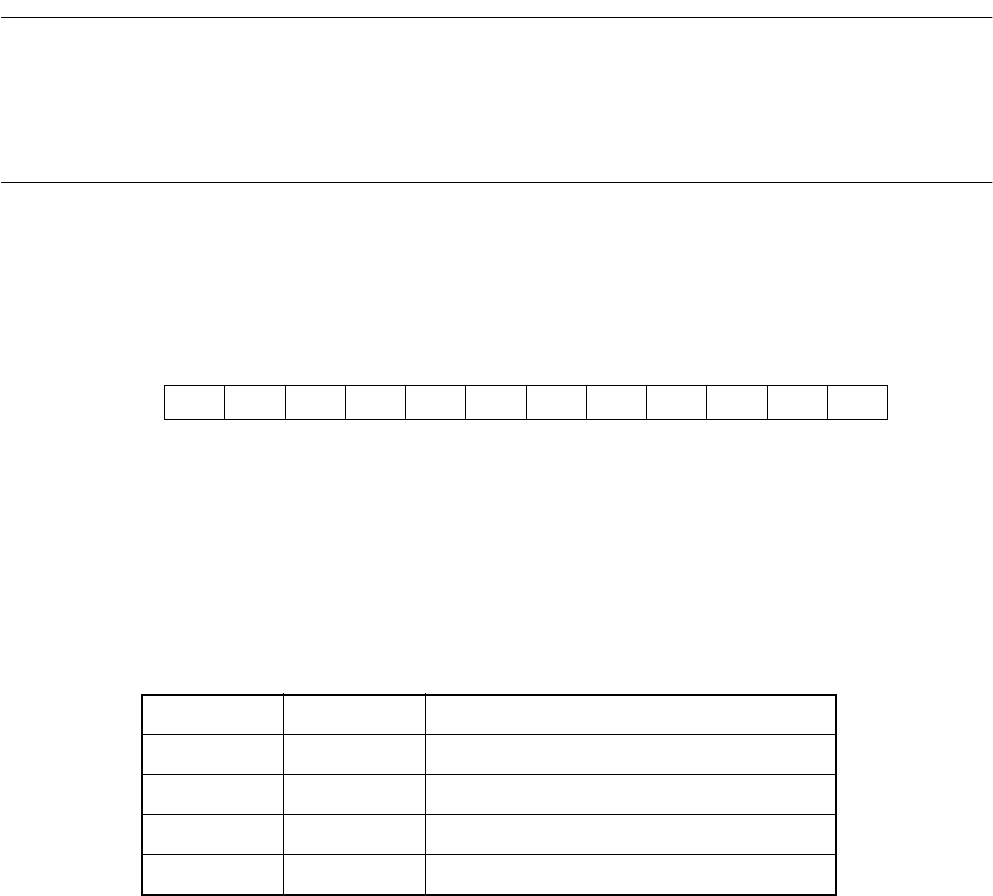

Configuration of Control Status Register (TMCSR)

The configuration of the control status register (TMCSR) is shown below:

■

Bit Functions of Control Status Register (TMCSR)

[bits 11, 10] CSL1, CSL0 (Count clock SLect)

These bits are used to select the count clock.

Table 12.2-1 lists the clock sources that can be selected.

[bits 9, 8, 7] MOD2, MOD1, MOD0 (MODe)

These bits specify the operation mode.

Always set these bits to "0".

[bit 6] OUTE (OUTput Enable)

Always set this bit to "0".

[bit 5] OUTL

Always set this bit to "0".

[bit 4] RELD

This is a reload enable bit. Setting this bit to "1" enables the reload mode. When the

counter value underflows from 0000

H

to FFFF

H

in reload mode, the value in the reload

register is loaded to the counter and the counter continues counting. When the counter

value underflows 0000

H

to FFFF

H

while the bit is "0", the counter stops counting.

11109876543210

TMCSR

Address:00002E

H

CSL1 CSL0 MOD2 MOD1 MOD0 OUTE OUTL RELD INTE UF CNTE TRG

000036

H

-000

H

000042

H

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Initial value

Table 12.2-1 CSL Bit Setting Clock Source

CSL1 CSL0 Clock source (

φ:

φ:φ:

φ:

machine clock)

00

φ

/2

1

01

φ

/2

3

10

φ

/2

5

11 Reserved