330

CHAPTER 15 DMAC

■

Bit Functions of DMAC Pin Control Register (DATCR)

[bit 21,20, 13, 12, 5, 4] LSn1, LSn0: Transfer request input detect level select

Each of these bits selects the detection level of the corresponding external transfer request

input pin DREQn as shown in Table 15.4-1.

The values of these bits are undefined after resetting.

The bits can be both read and written.

When continuous transfer mode is used, set the bits for "H" level or "L" level detection.

[bit 19, 11, 3] AKSEn

[bit 18, 10, 2] AKDEn

These bits specify the time when the transfer request acknowledgment output signal is to be

generated from the corresponding output pin and specify whether to enable the output

function of the corresponding transfer request acknowledgment output signal pin.

These bits are initialized to "00" by resetting.

The bits can be both read and written.

[bit 17, 9, 1] EPSEn

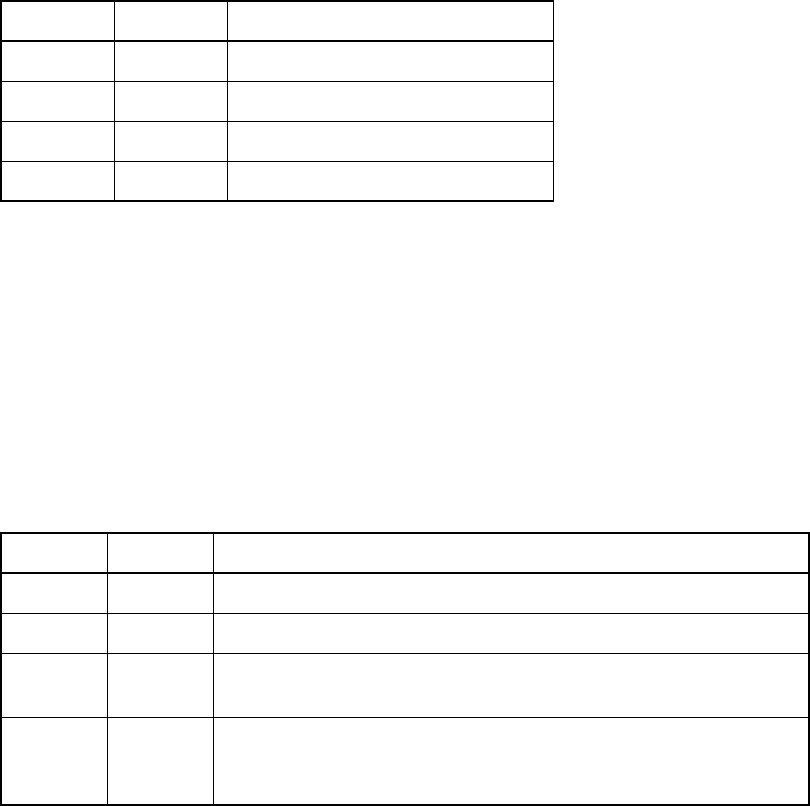

Table 15.4-1 Selection of Transfer Input Detection Levels

LSn1 LSn0 Operation control function

0 0 Detection of rising edge

0 1 Detection of falling edge

1 0 Detection of H level

1 1 Detection of L level

Table 15.4-2 Specification of Transfer Request Acknowledgment Output

AKSEn AKDEn Operation control function

0 0 Disables transfer request acknowledgment output.

0 1 Enables transfer request acknowledgment output.

1 0 Acknowledgement is output when transfer destination data is

accessed.

1 1 Enables transfer request acknowledgment output.

Acknowledgement is output when transfer source and

destination data is accessed.