332

CHAPTER 15 DMAC

15.5 Descriptor Register in RAM

This descriptor register has the setup information for the corresponding channel in

DMA transfer mode.

The descriptor register has a 12-byte area for each channel that is allocated to the

memory address specified by DPDP.

See Table 15.2-1, " Channel descriptor addresses," for the first address of the

descriptor for each channel.

■

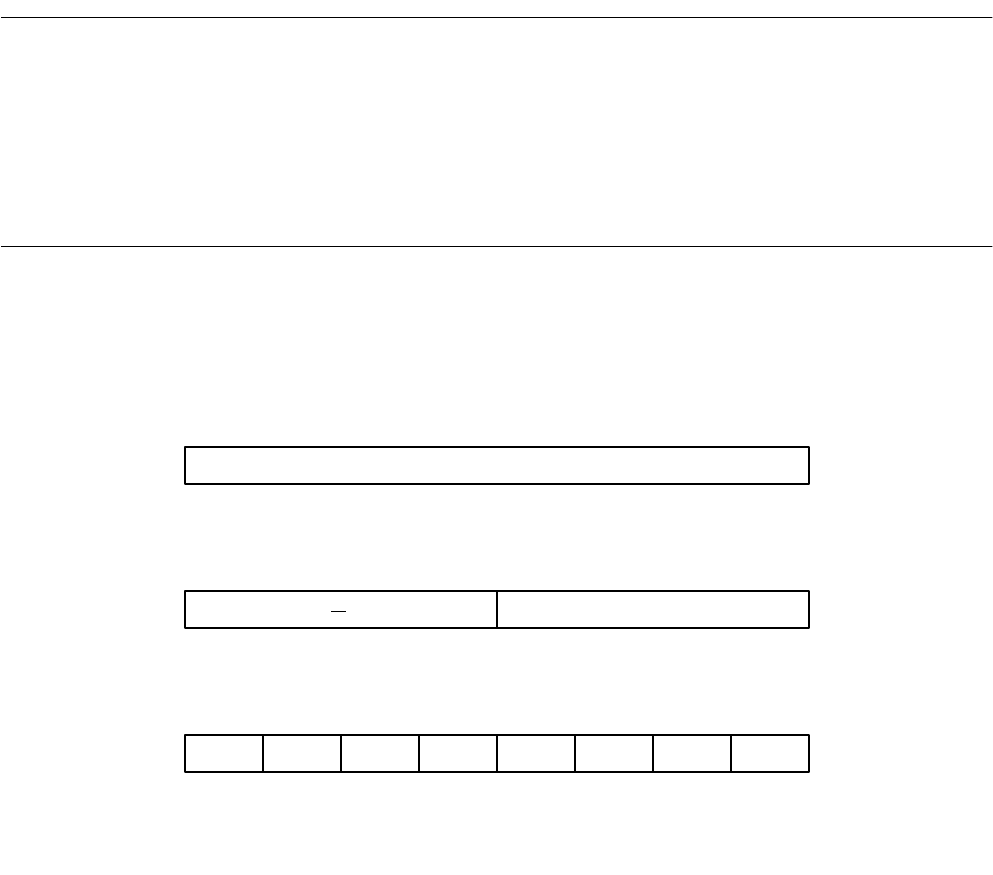

First Word of a Descriptor

The structure of the first word of a descriptor is shown below.

[bits 31 to 16] DMACT: Transfer count

These bits specify the number of times DMA transfer is to be performed. When 0000H is

specified, DMA transfer is performed 65,536 times.

The value is decremented by 1 each time DMA transfer is performed.

[bits 15 to 12] Reserved

[bits 11 to 8] BLK: Block size specification

These bits specify the size of blocks to be transferred in single/block transfer mode.

When 0 is specified, a block size of 16 is assumed.

Specify 1 for single transfer.

[bits 7, 6] SCS1, SCS0: Transfer source address update mode

31 16

R/W

15 14 13 12 11 10 9 8

R/W

7654 3210

R/W R/W R/W R/W R/W R/W R/W R/W

DMACT

DCS0DCS1SCS0SCS1 WS0 MOD1WS1

BLK

MOD0

Initial value: undefined