383

APPENDIX C Pin Status for Each CPU Status

APPENDIX C Pin Status for Each CPU Status

Table C.1 explains the terms used in the pin status list. Table C-2 to Table C-5 list the

pin status for each CPU status.

Note that the pin status at reset differs between the external bus mode and single chip

mode.

■

Explanation of Terms Used in the Pin Status List

The terms used in the pin status list are explained below.

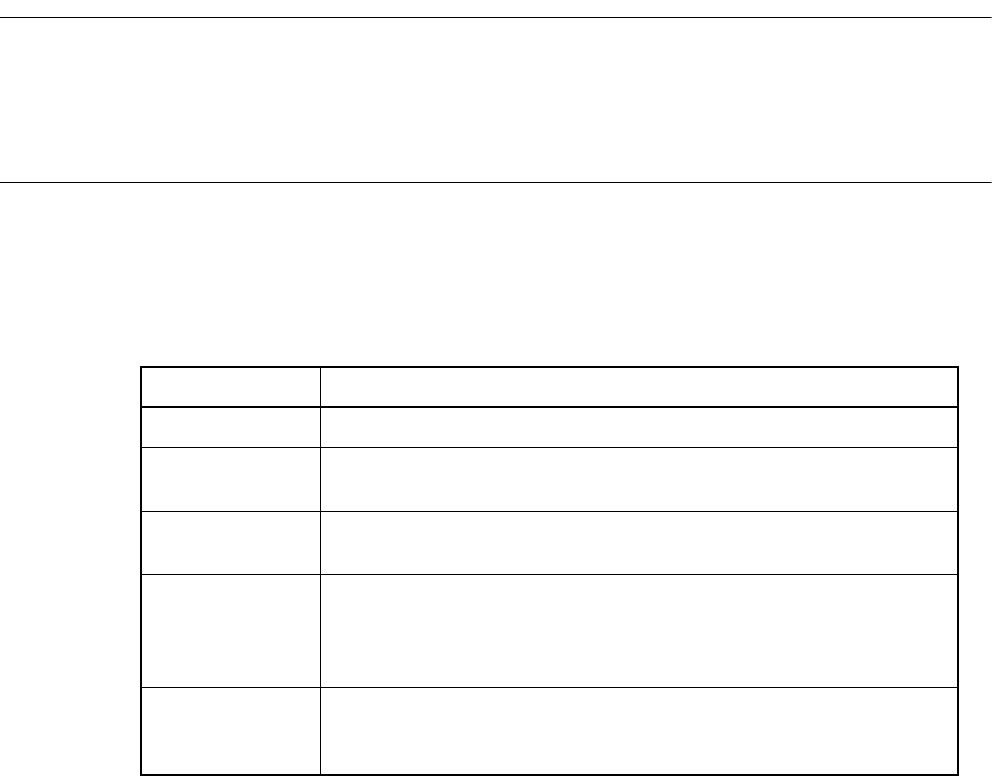

Table C-1 Explanation of Terms Used in the Pin Status List

Term Explanation

Input possible Input functions are ready to use.

Input fixed to 0 External inputs are blocked out and the value “0” is transmitted

internally from the input gate near the pin.

Output Hi-Z Pin drive transistors are put in drive-inhibited status, and their pins

are put in high-impedance status.

Output retained The output status immediately before this mode is entered is output

unchanged. For example, if an internal peripheral component with

an output is operating, this output is not inhibited. In case of an

output to a port, this output is retained.

The previous

status is retained

The output status immediately before this mode is entered is output

unchanged. Inputs are not inhibited either, and are processed

accordingly.