101

3.12 Reset Source Hold Circuit

3.12 Reset Source Hold Circuit

The reset source hold circuit holds the source of previous resetting. Reading the

circuit clears all flags to 0. Once a source flag is set, it is not cleared unless the circuit

is read.

■

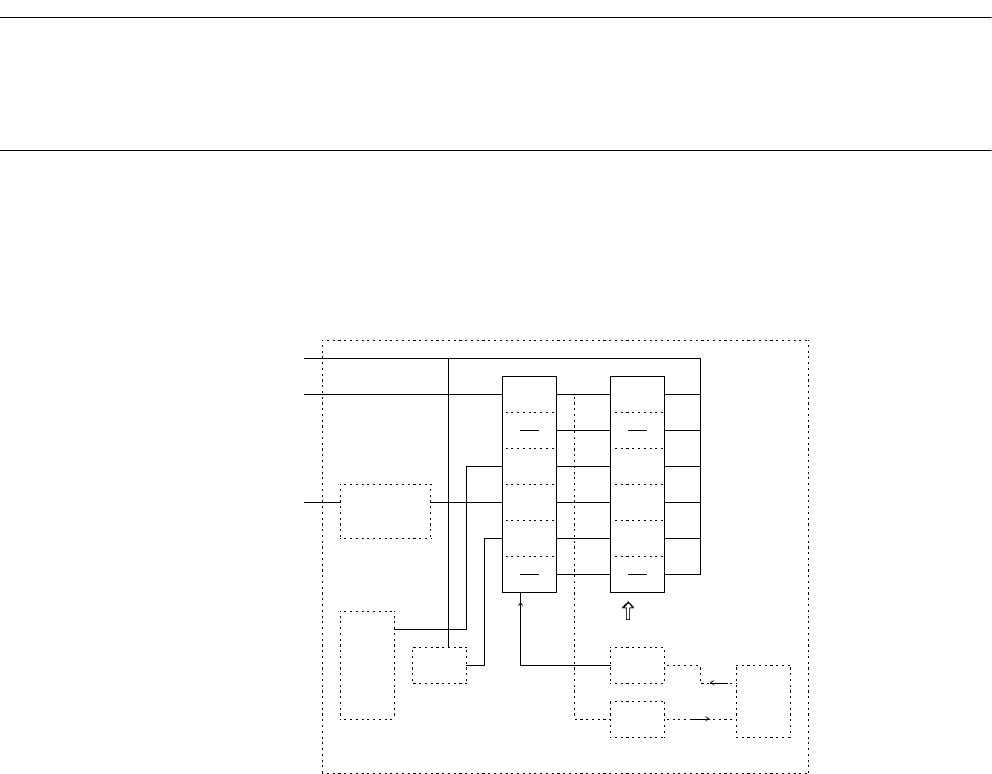

Block Diagram of Reset Source Hold Circuit

Figure 3.12.1 is a block diagram of the reset source hold circuit.

Figure 3.12-1 Block Diagram of Reset Source Hold Circuit

■

Setting for Reset Source Holding

No special settings are required to use the reset source hold function. Provide an instruction to

read the reset source register and an instruction to branch to the appropriate program, at the

beginning of the program to be placed at the reset entry address.

PONR

PONR

WDOG

WDOG

ERST

ERST

SRST

SRST

clr

SRST

STCR

.or.

Internal bus

From power-on cell

RSTX pin

RSTX

input circuit

Watchdog reset

detection circuit

State = RST

Initialized

by reading

Decoder

State

transi-

tion

circuit