61

2.8 EIT (Exception, Interrupt, and Trap)

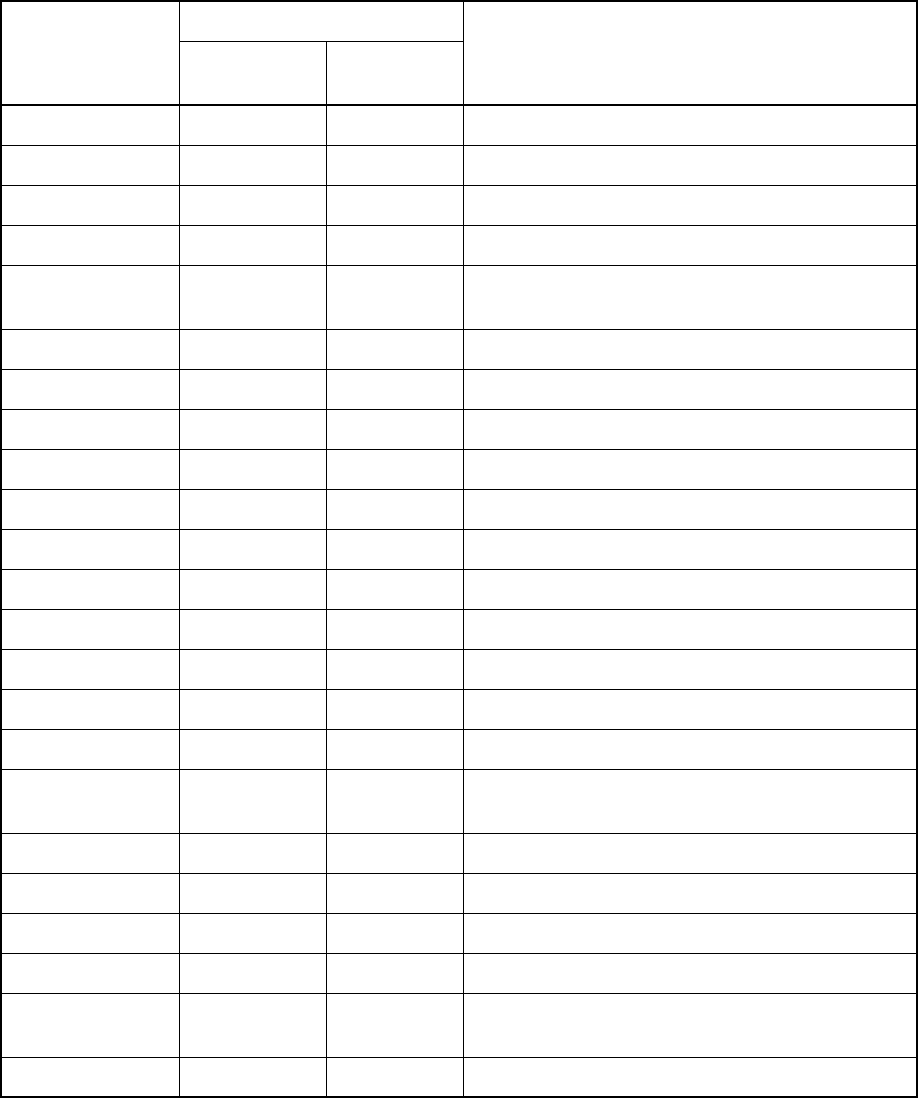

Table 2.8.3 is the vector table in the architecture.

Special functions are assigned to some vectors.

Table 2.8-3 Vector Table

Vector offset

(hexadecimal)

Vector number Explanation

Hexadecima

l

Decimal

3FC 00 0 Reset (*1)

3F8 01 1 Reserved by the system

3F4 02 2 Reserved by the system

3F0 03 3 Reserved by the system

:

:

:

:

:

:

:

:

3E0 07 7 Reserved by the system

3DC 08 8 Reserved by the system

3D8 09 9 INTE instruction

3D4 0A 10 Reserved by the system

3D0 0B 11 Reserved by the system

3CC 0C 12 Step-trace-trap

3C8 0D 13 Reserved by the system

3C4 0E 14 Undefined-instruction exception

3C0 0F 15 NMI (for user)

3BC 10 16 Maskable interrupt cause #0

3B8 11 17 Maskable interrupt cause #1 *

2

:

:

:

:

:

:

:

:

300 3F 63 Maskable interrupt cause/INT instruction

2FC 40 64 Reserved by the system (used for REALOS)

2F8 41 65 Reserved by the system (used for REALOS)

2F4 42 66 Maskable interrupt cause/INT instruction

:

:

:

:

:

:

:

:

000 FF 255

*1: Fixed address 000FFFFC

H

is always used for the reset vector even when the TBR value is changed.

*2: See Appendix B, "Interrupt Vector," for the vector table for the MB91F109.