147

4.16 Relationship between Data Bus Widths and Control Signals

4.16.2 Bus Access with Little Endians

When external bus access is performed for areas set by the little endian register (LER),

those areas are handled as little endians.

■

Outline of Little Endians

Little endian bus access by the MB91F109 uses the bus access operation for big endians. The

address output sequence and control signal output for big endians are basically the same as

those for little endians, which are implemented by swapping data bus byte locations according

to the bus width.

When the devices are connected, exercise extreme caution, as the big and little endian areas

must be physically separated.

• The address output sequence is the same for both big and little endians.

• Word access: The MSB-side byte data, which corresponds to address 00 of big endians, is

the LSB-side data for little endians.

In word access, all 4 bytes in the word are binary inverted.

"00" --> "11", "01" --> "10", "10" --> "01", "11" --> "00"

• Half-word access: The MSB-side byte data, which corresponds to address 00 of big

endians, is the LSB-side byte data for little endians.

In half-word access, all locations of 2 bytes in a half-word are exchanged for those having an

opposite value.

"0" --> "1", "1" --> "0"

• Byte access: Same for both big and little endians

• The data bus control signals used in a 16/8 bit bus width are the same for both big and little

endians.

■

Data Format

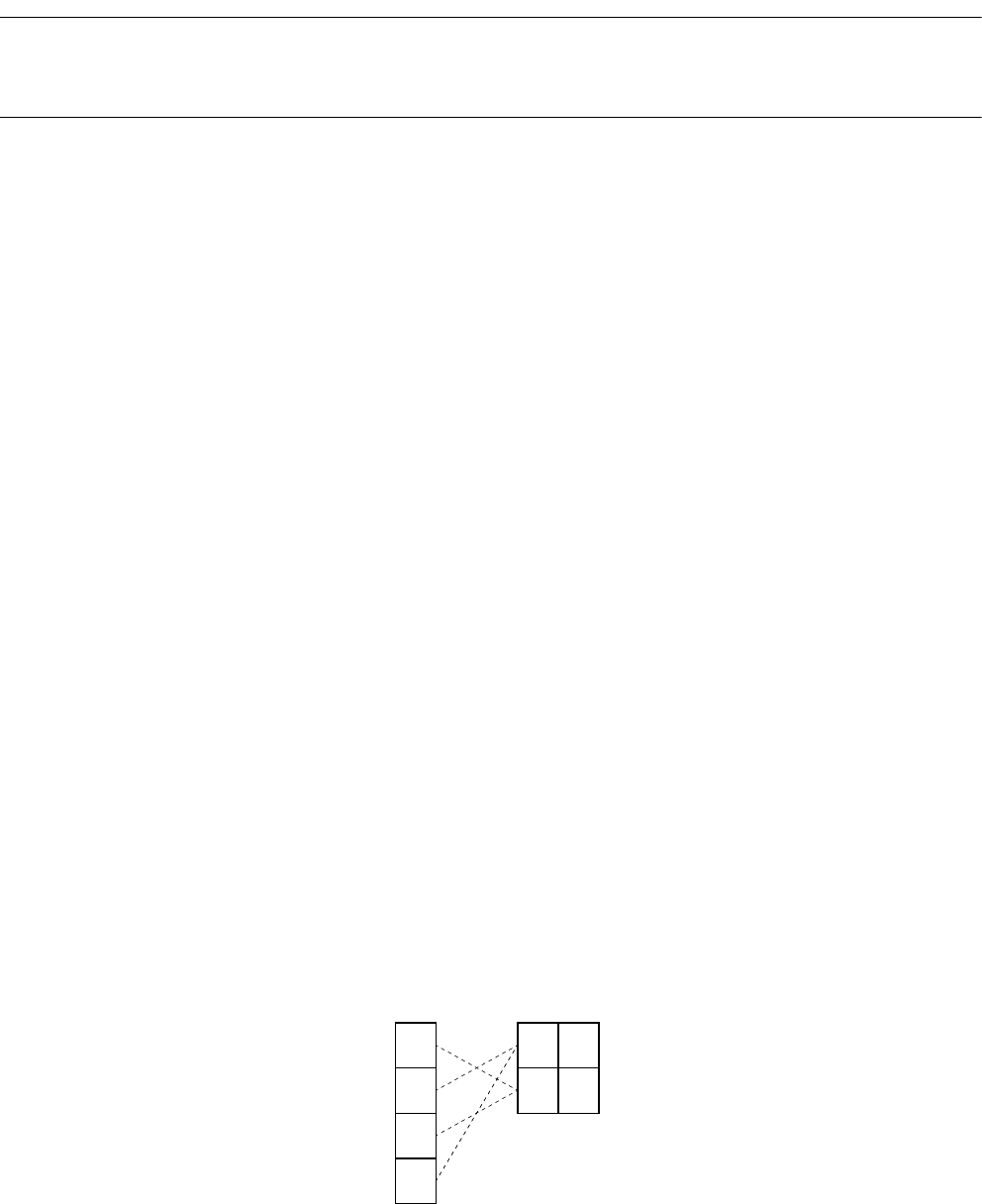

The following shows the relationship between the internal register and external data bus in each

data format:

❍

Word access (during execution of LD and ST instructions)

Figure 4.16-11 Relationship between Internal Register and External Data Bus for Word Access

AA DD BB

BB CC AA

CC

DD

D31

D07

D15

D23

D31

D23

Internal register External bus