232

CHAPTER 8 INTERRUPT CONTROLLER

DMAC 2 (end, error) 28 1C ICR12 38C

H

000FFF8C

H

DMAC 3 (end, error) 29 1D ICR13 388

H

000FFF88

H

DMAC 4 (end, error) 30 1E ICR14 384

H

000FFF84

H

DMAC 5 (end, error) 31 1F ICR15 380

H

000FFF80

H

DMAC 6 (end, error) 32 20 ICR16 37C

H

000FFF7C

H

DMAC 7 (end, error) 33 21 ICR17 378

H

000FFF78

H

A/D 34 22 ICR18 374

H

000FFF74

H

Reload timer 0 35 23 ICR19 370

H

000FFF70

H

Reload timer 1 36 24 ICR20 36C

H

000FFF6C

H

Reload timer 2 37 25 ICR21 368

H

000FFF68

H

PWM 0 38 26 ICR22 364

H

000FFF64

H

PWM 1 39 27 ICR23 360

H

000FFF60

H

PWM 2 40 28 ICR24 35C

H

000FFF5C

H

PWM 3 41 29 ICR25 358

H

000FFF58

H

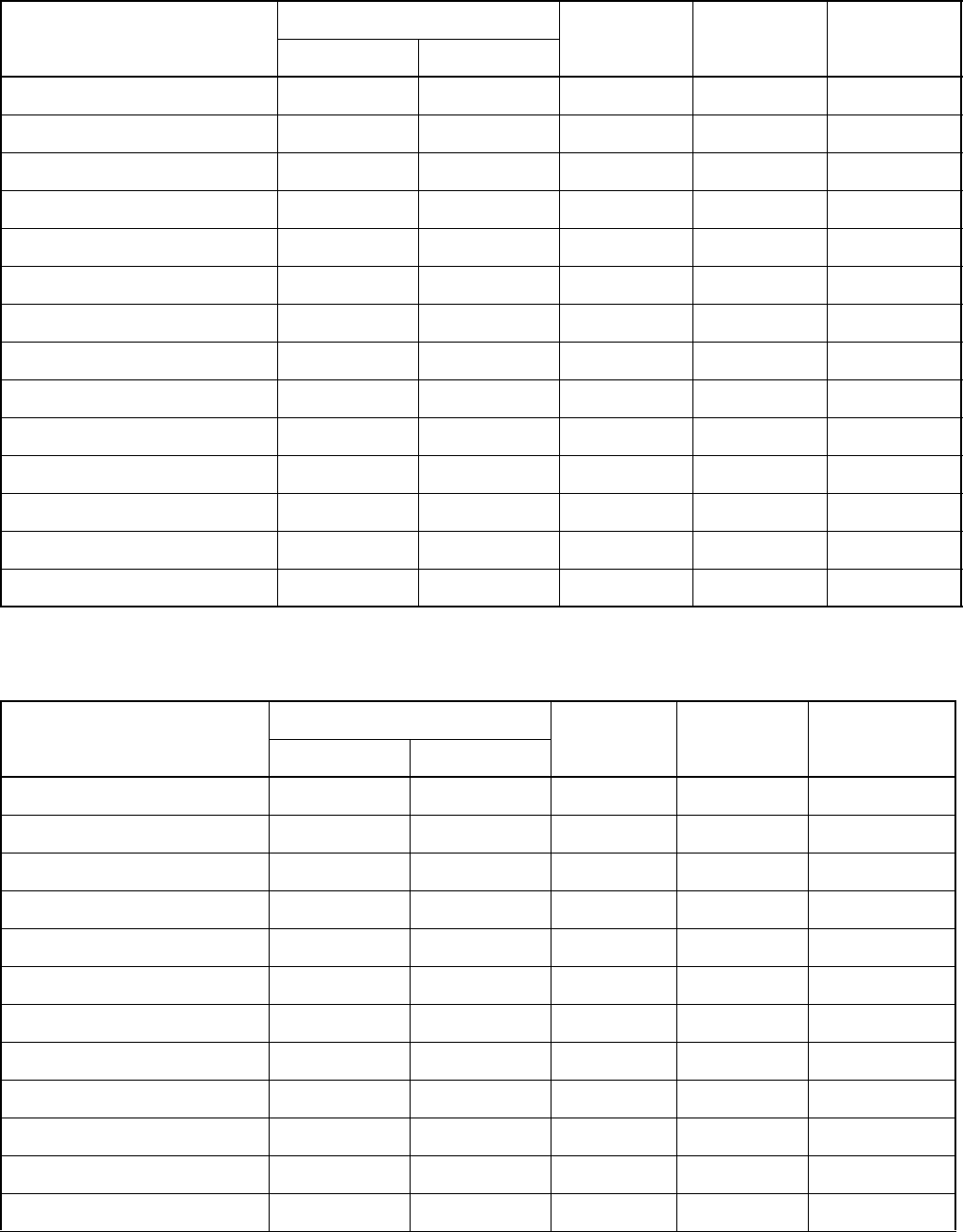

Table 8.5-1 Relationships among Interrupt Causes, Numbers, and Levels (1/2)

Cause of interrupt Interrupt number Interrupt

level

Offset TBR default

address

Decimal Hexadecimal

Table 8.5-2 Relationships among Interrupt Causes, Numbers, and Levels (2/2)

Cause of interrupt Interrupt number Interrupt

level

Offset TBR default

address

Decimal Hexadecimal

U-TIMER 0 42 2A ICR26 354

H

000FFF54

H

U-TIMER 1 43 2B ICR27 350

H

000FFF50

H

U-TIMER 2 44 2C ICR28 34C

H

000FFF4C

H

Flash memory 45 2D ICR29 348

H

000FFF48

H

Reserved by the system 46 2E ICR30 344

H

000FFF44

H

Reserved by the system 47 2F ICR31 340

H

000FFF40

H

Reserved by the system 48 30 - 33C

H

000FFF3C

H

Reserved by the system 49 31 - 338

H

000FFF38

H

Reserved by the system 50 32 - 334

H

000FFF34

H

Reserved by the system 51 33 - 330

H

000FFF30

H

Reserved by the system 52 34 - 32C

H

000FFF2C

H

Reserved by the system 53 35 - 328

H

000FFF28

H