100

CHAPTER 3 CLOCK GENERATOR AND CONTROLLER

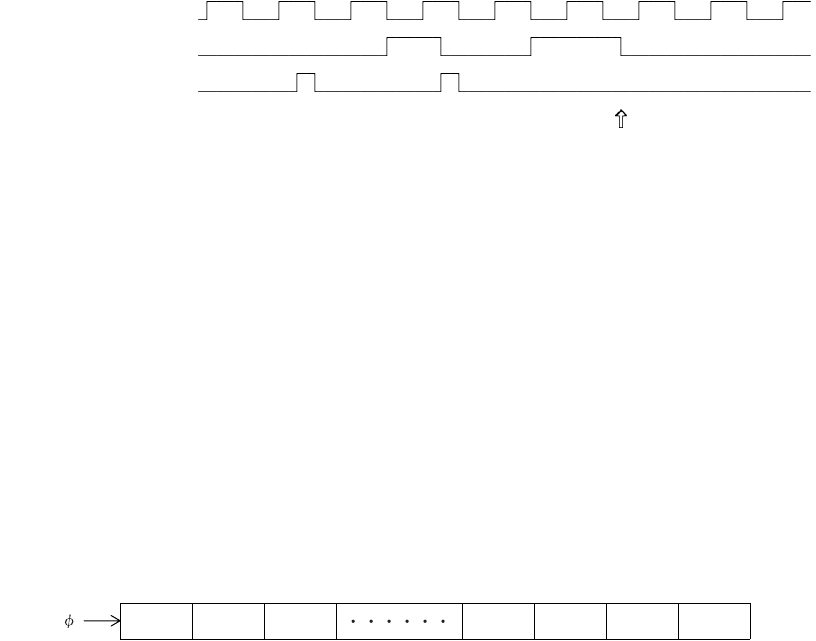

Figure 3.11-2 Watchdog Timer Operating Timing

<Note>

• The time interval between the first A5

H

and the next 5A

H

is not specified. Watchdog

resetting is postponed only if the time interval from one 5A

H

to the next 5A

H

is within the time

specified by the WT bits and one A5

H

is written between them.

• If the first A5

H

is followed by something other than 5A

H

, the first A5

H

is ignored. Therefore,

A5

H

must be written again.

■

Timebase Timer

The timebase timer is used to supply clock pulses to the watchdog timer and is used also as the

oscillation stabilization wait timer. The operating clock

φ

is double the X0 when the GCR CHC is

1 or the cycle of the PLL oscillation frequency when the GCR CHC is 0.

The value of this timebase timer is set in the RFCR and used as the count clock for the count

value for DRAM refresh.

Figure 3.11-3 Timebase Timer Counter

Watchdog start

Watchdog clear

Watchdog resetting

Timebase timer overflow

Watchdog flip-flop

WTE write

1/2

1

1/2

2

1/2

3

1/2

18

1/2

19

1/2

20

1/2

21