320

CHAPTER 14 PWM TIMER

14.12Constant "L" or Constant "H" Output from PWM Timer

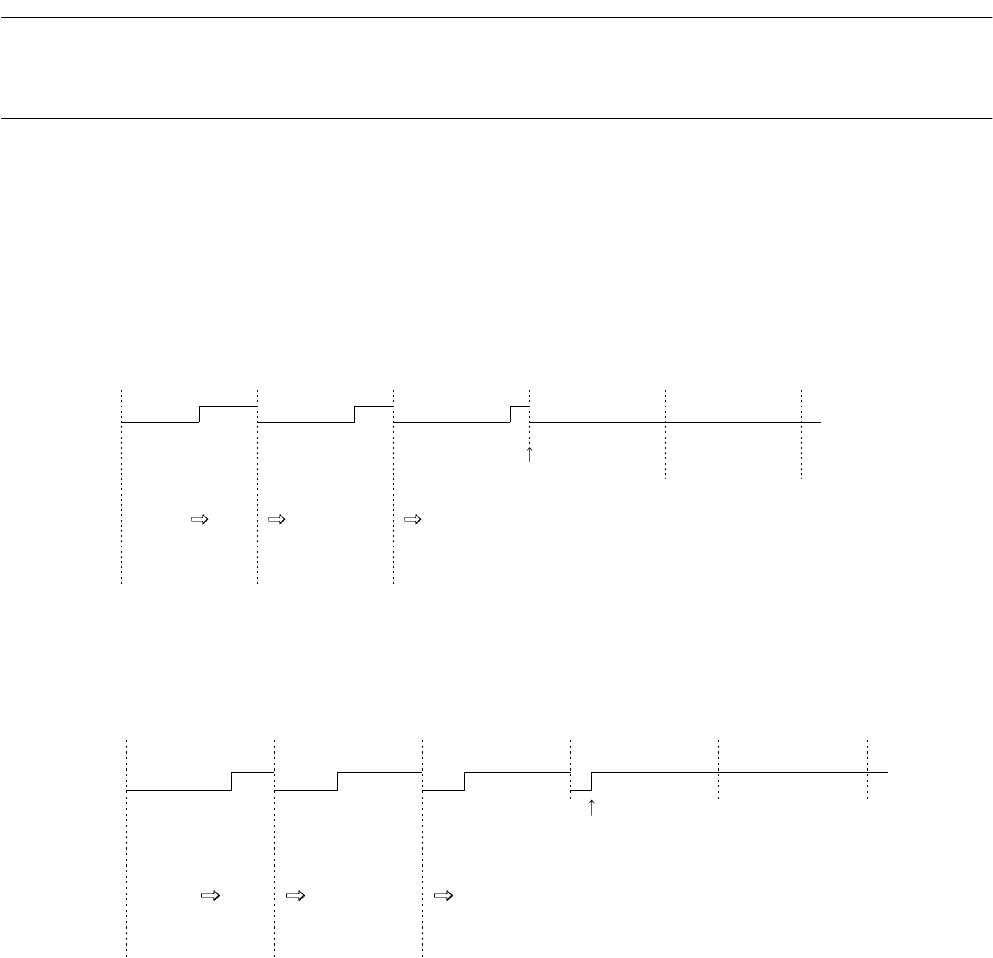

Figure 14.12-1 shows how the PWM timer can keep output at a low level. Figure 14.12-

2 shows how the PWM timer can keep output at a high level.

■

Constant "L" or Constant "H" Output from PWM Timer

❍

Example of keeping PWM output at a lower level

Figure 14.12-1 Example of Keeping PWM Output at a Lower Level

❍

Example of keeping PWM output at a high level

Figure 14.12-2 Example of Keeping PWM Output at a High Level

PWM

Decrease the duty

value gradually.

An interrupt generated by a borrow causes "1" to be written to

PGMS (mask bit).

If an interrupt generated by a borrow causes "0" to be written to

PGMS (mask bit), PWM waveforms can be output with no whisker.

PWM

Increase the duty

value gradually.

An interrupt generated by a compare match causes

the same value as that in the cycle setting register to

be written to the duty cycle setting register.