217

6.6 External Interrupt Request Levels

6.6 External Interrupt Request Levels

When an edge is selected for the interrupt request mode, a pulse width of at least three

machine cycles (peripheral clock machine cycles) is required to detect an edge.

When a level is selected for the interrupt request mode, an external request that has

been input may be canceled later, though the request issued to the interrupt controller

remains active because an interrupt cause hold circuit exists inside.

The interrupt request register must be cleared to cancel the request issued to the

interrupt controller.

■

External Interrupt Request Levels

Figure 6.6-1 shows how the interrupt cause hold circuit is cleared when a level is selected for

the interrupt request mode. Figure 6.6-2 shows the input of an interrupt cause in interrupt

enable mode and a request issued to the interrupt controller.

Figure 6.6-1 Clearing the Interrupt Cause Hold Circuit at Level Setting for the Interrupt Request Mode

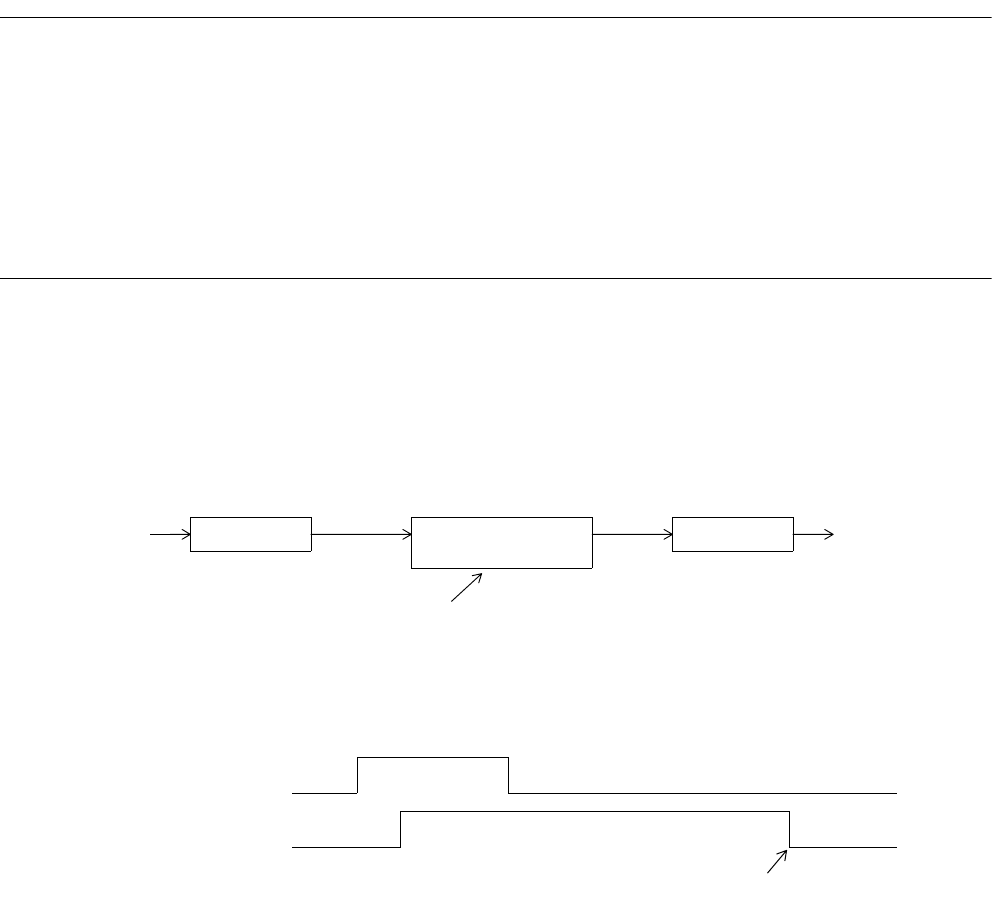

Figure 6.6-2 Input of an Interrupt Cause in Interrupt Enable Mode and a Request Issued to the Interrupt

Controller

Level

detection

Input of interrupt

Cause F/F

(cause hold circuit)

The cause is held until the flip-flop is cleared.

Enable gate

To the interrupt

controller

H level

Interrupt request to

the interrupt controller

Input of interrupt

Clearing the interrupt cause flip-flop deactivates the signal.