388

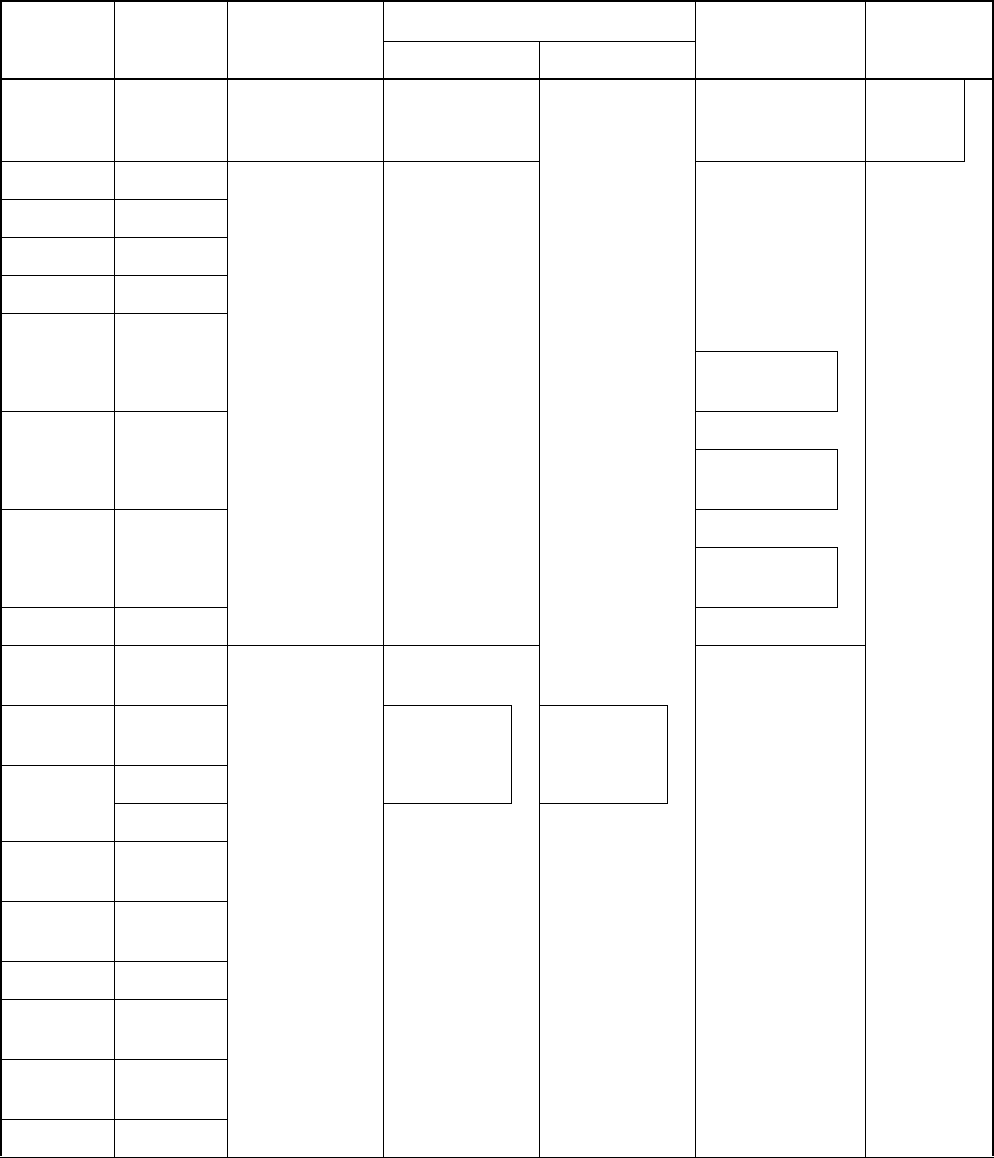

APPENDIX C Pin Status for Each CPU Status

PA6 CLK P: Previous

status retained

F: CLK output

P, F: Previous

status retained

Output Hi-Z/

Input fixed to 0

CLK Output CLK

Output

PB0 RAS0 P: Previous

status retained

F: Previous

value retained

Executed when

DRAM pin is

set.

P: Previous

status retained

F: Previous

value retained

During refresh

(*1)

P: Previous

status retained

F: Previous value

retained

Operation during

DRAM terminal

setting

Output Hi-Z/

Input

allowed for

all pins

PB1 CS0L

PB2 CS0H

PB3 DW0X

PB4 RAS1

EOP2 Previous

value retained

PB5 CS1L

DREQ2 Previous

value retained

PB6 CS1H

DACK2 Previous

value retained

PB7 DW1X

AN0 to

AN3

AN0-3 Previous status

retained

Previous status

retained

PE0 to

PE2

INT0-INT2 Input

possible

Input

possible

PE3 INT3

SC2 Previous status

retained

PE4 to

PE5

DREQ0-

DREQ1

PE6 to

PE7

DACK0-

DACK1

PF0 SI0, TRG0

PF1 SO0,

TRG1

PF2 SC0,

OCPA3

PF3 SI1, TRG2

Table C-3 Pin Status for 16-bit External Bus Length and 2CA1WR Mode (Continued)

Pin name Function During sleep During stop Bus release

(BGRNT)

Reset time

HIZX=0 HIZX=1