261

10.9 UART Interrupt Occurrence and Flag Setting Timing

■

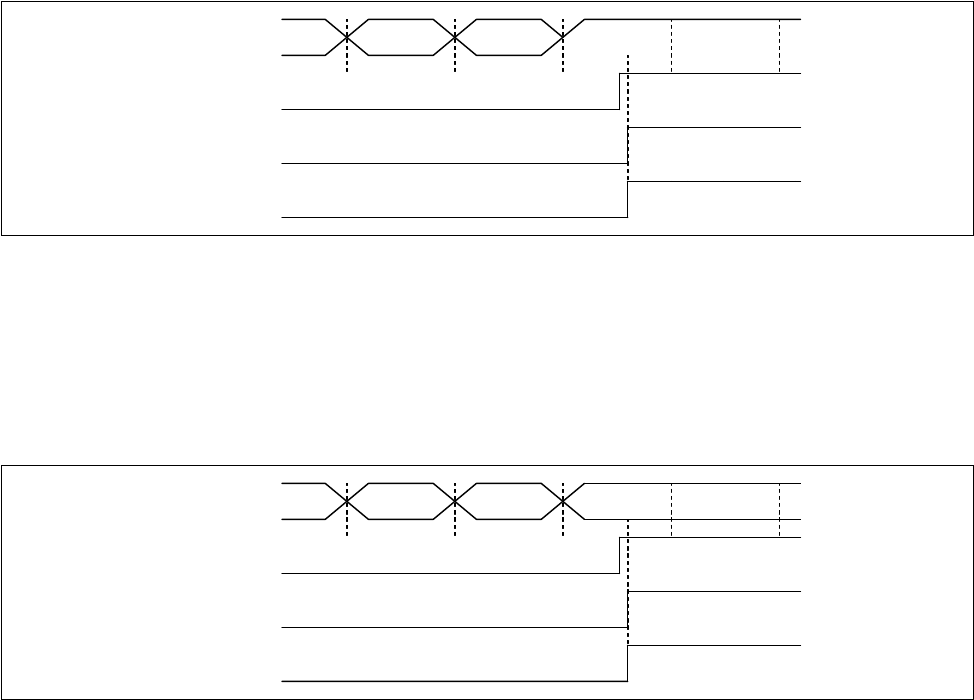

Interrupt Flag Set Timing for Data Recepion in Mode 1

When the last stop bit is detected after data reception/transfer is completed, the ORE, FRE, and

RDRF flags are set to issue an interrupt request to the CPU. Since the length of data items that

can be received is eight bits, the data at the last bit, bit 9, indicates an address or that data is

invalid. If ORE or FRE is active, the SIDR data is invalid.

Figure 10.9-2 ORE, FRE, and RDRF Set Timing (Mode 1)

■

Interrupt Flag Set Timing for Data Reception in Mode 2

When the last data item (D7) is detected after data reception/transfer is completed, the ORE

and RDRF flags are set to issue an interrupt request to the CPU. If ORE is active, the SIDR

data is invalid.

Figure 10.9-3 ORE and RDRF Set Timing (Mode 2)

D7 Stop

ORE, FRE

RDRF

Reception interrupt

Data

Address/

data

D5 D6 D7

ORE

RDRF

Reception interrupt

Data