158

CHAPTER 4 BUS INTERFACE

■

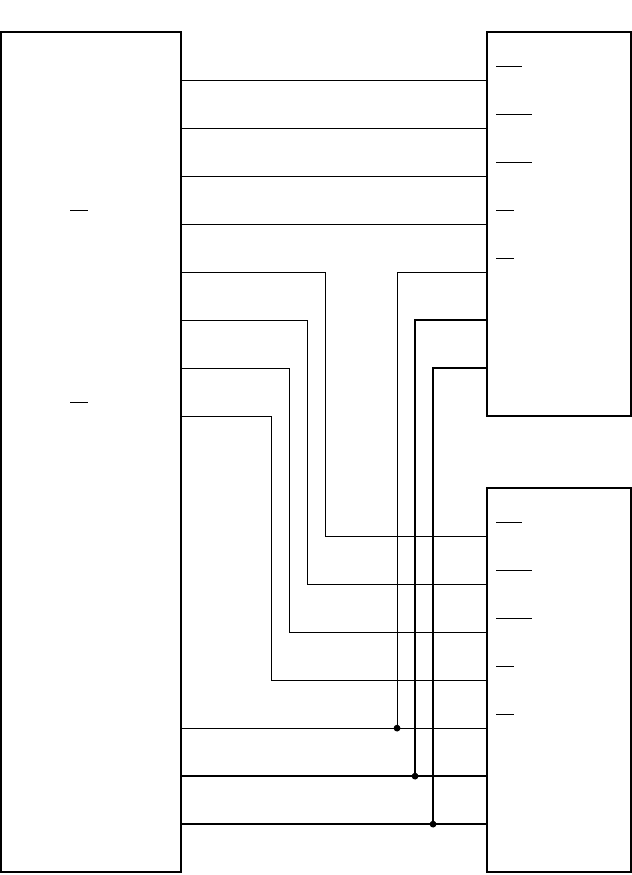

Connection Example of DRAM Device

• DRAM: 2CAS/1WE, page size 512, × 16-bit product

• Bus width: 16 bits

• Number of banks: 2 (areas 4 and 5)

Figure 4.16-20 Example of Connection between MB91F109 and Two 16-Bit Output DRAMs (16-Bit Data

Bus)

(Area4 RAS) RAS0 RAS

(Area4 CASL) CSOL UCAS

(Area4 CASH)CS0H LCAS

(Area4 WE) DW0X WE

(Area5 RAS) RAS1 OE

(Area5CASL) CS1L A8-A0

(Area5CASH) CS1H D16-D1

(Area5 WE) DW1X

RAS

UCAS

LCAS

WE

RDX OE

(A00 not

connected)

A09-01 A8-A0

D31-16 D16-D1

Area 4 DRAM

Area 5 DRAM

This LSI