415

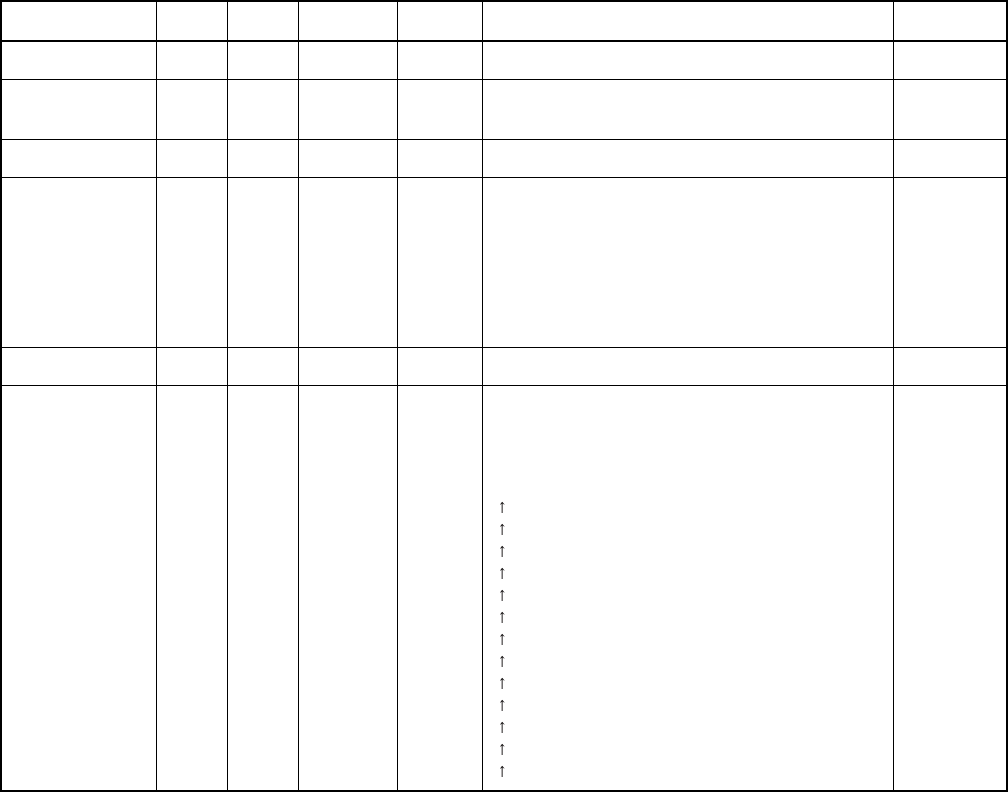

APPENDIX E Instructions

■

Standard Branch (Without Delay) Instructions

(Notes)

• The number of cycles item "2/1" means 2 cycles for branch and 1 for nonbranch.

• The assembler calculates and sets values in the rel11 and rel8 fields of the hardware

specifications as follows:

(label12-PC-2)/2 -> rel11, (label9-PC-2)/2 -> rel8: Label12 and label9 are signed.

• When RETI is executed, the S flag must be “0”.

Table E.1-11 Standard Branch (Without Delay) Instructions

Mnemonic Type OP CYCLE NZVC Operation Remarks

JMP @Ri E 97-0 2 ---- Ri --> PC

CALL label12

CALL @Ri

F

E

D0

97-1

2

2

----

----

PC+2-->RP ,PC+2+(label12-PC-2) -->PC

PC+2-->RP ,Ri-->PC

RET E 97-2 2 ---- RP --> PC Return

INT #u8

INTE

D

E

1F

9F-3

3+3a

3+3a

----

----

SSP-=4,PS-->(SSP),SSP-=4,PC+2-->(SSP),

0-->I flag,0-->S flag

(TBR+0x3FC-u8×4) -->PC

SSP-=4,PS-->(SSP),SSP-=4,PC+2-->(SSP),

0-->S flag,(TBR+0×3D8) -->PC

For the

emulator

RETI E 97-3 2+2a CCCC (R15) -->PC,R15-=4,(R15) -->PS,R15-=4

BRA label9

BNO label9

BEQ label9

D

D

D

E0

E1

E2

2

1

2/1

----

----

----

PC+2+(label9-PC-2) -->PC

Nonbranch

if(Z==1) then

PC+2+(label9-PC-2) -->PC

BNE label9

BC label9

BNC label9

BN label9

BP label9

BV label9

BNV label9

BLT label9

BGE label9

BLE label9

BGT label9

BLS label9

BHI label9

D

D

D

D

D

D

D

D

D

D

D

D

D

E3

E4

E5

E6

E7

E8

E9

EA

EB

EC

ED

EE

EF

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

----

----

----

----

----

----

----

----

----

----

----

----

----

s/Z==0

s/C==1

s/C==0

s/N==1

s/N==0

s/V==1

s/V==0

s/V xor N==1

s/V xor N==0

s/(V xor N) or Z==1

s/(V xor N) or Z==0

s/C or Z==1

s/C or Z==0