186

CHAPTER 4 BUS INTERFACE

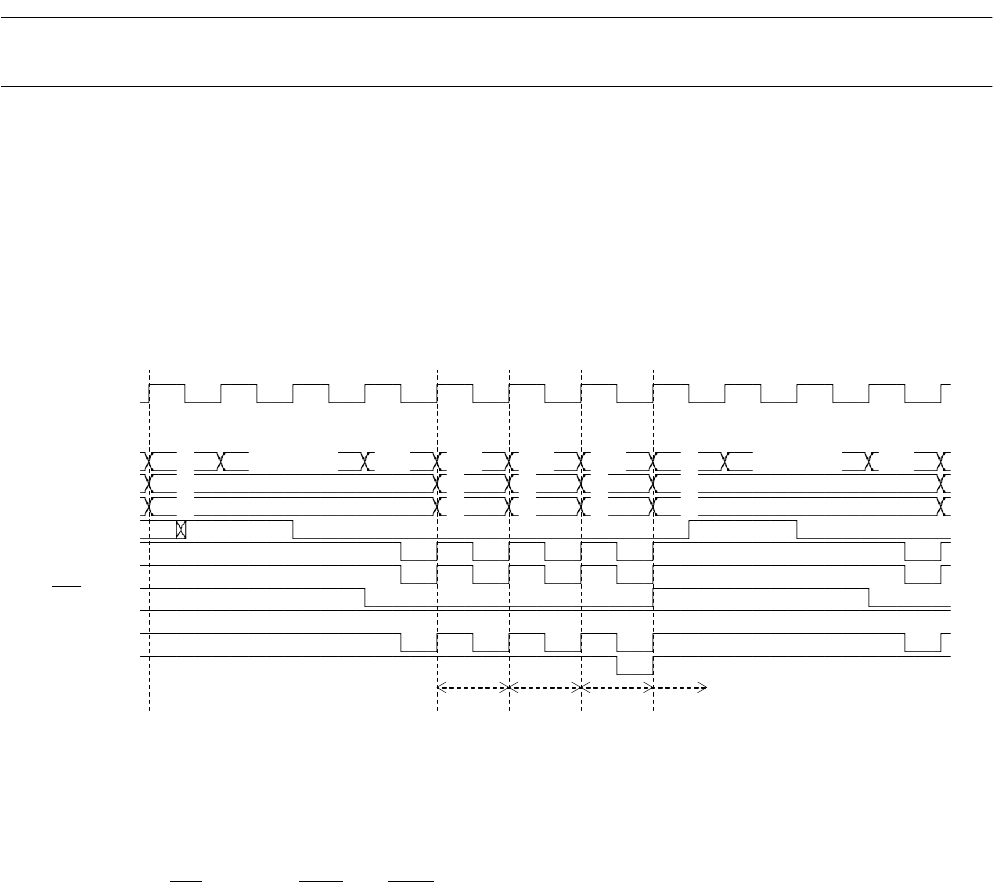

4.17.15 Single DRAM Interface: Write

This section provides a single DRAM interface write timing chart.

■

Single DRAM Interface: Write Timing Chart

❍

Bus width: 16 bits, access: words

Figure 4.17-30 Example of Single DRAM Interface Write Timing Chart

[Explanation of operation]

• Column addresses and write data are output in Q4SW cycles.

• CAS is asserted at the falling edge of Q4SW and negated at the rising edge or end of the

Q4SW cycle.

•WE

(including WEL and WEH) is asserted at the rising edge of the Q4SW cycle and negated

when Q4SW ends.

Q1 Q2 Q3 Q4SW Q4SW Q4SW Q4SW Q1 Q2 Q3 Q4SW

CLK

2)2CAS/1WE

A24-00

X row.adr. col. col. col. col. X row.adr. col.

D31-24 W W W W W

D23-16 W W W W W

RAS

CASL

CASH

WE

RDX

(DACK0)

(EOP0)

High speed

page

High speed

page

High speed

page