8 ELECTRICAL CHARACTERISTICS

A-84 EPSON S1C33L03 PRODUCT PART

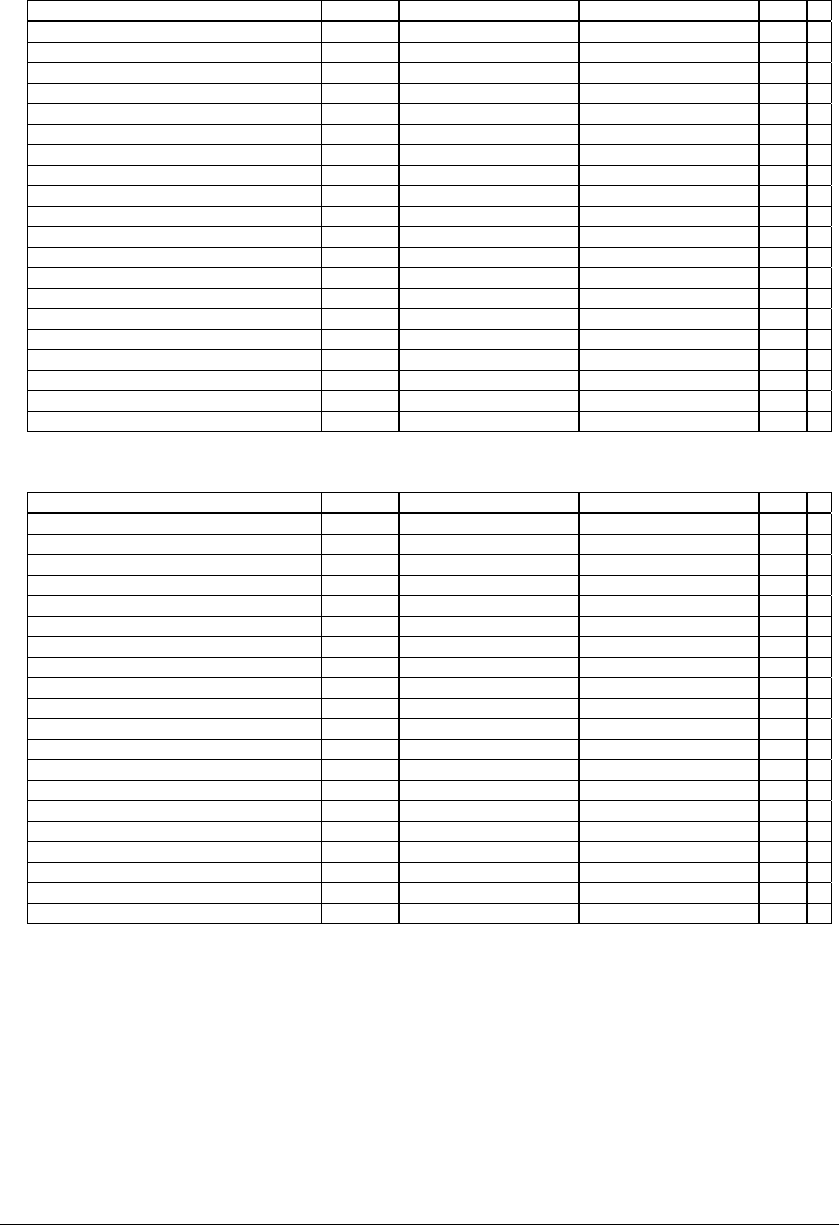

SDRAM access cycle

1) #X2SPD = "1" (CPU : SDRAM clock = 1 : 1), 3.3 V single power source

(Unless otherwise specified: VDDE=VDD=3.0V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

OSC3 input clock frequency fOSC3 25 MHz

BCLK clock output cycle time t(C3) 40 ns

Address delay time t(AD) 11 ns

SDA10 delay time t(A10D) 11 ns

#SDCEx delay time (1) t(CED)n 11 ns

#SDCEx delay time (2) t(CED)p 11 ns

#SDRAS signal delay time (1) t(RASD)n 12 ns

#SDRAS signal delay time (2) t(RASD)p 11 ns

#SDCAS signal delay time (1) t(CASD)n 11 ns

#SDCAS signal delay time (2) t(CASD)p 11 ns

HDQM, LDQM signal delay time (1) t(DQMD)n 11 ns

HDQM, LDQM signal delay time (2) t(DQMD)p 11 ns

SDCKE signal delay time (1) t(CKED)n 11 ns

SDCKE signal delay time (2) t(CKED)p 11 ns

#SDWE signal delay time (1) t(WED)n 11 ns

#SDWE signal delay time (2) t(WED)p 11 ns

Read data setup time t(RDS) (14) ns

Read data hold time t(RDH) (0) ns

Write data delay time t(WDD) 11 ns

Write data hold time t(WDH) T+11 ns

2) #X2SPD = "0" (CPU : SDRAM clock = 2 : 1), 3.3 V single power source

(Unless otherwise specified: VDDE=VDD=3.0V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

OSC3 input clock frequency fOSC3 17.5 MHz

BCLK clock output cycle time t(C3x2) 57 ns

Address delay time t(ADx2) T+11 ns

SDA10 delay time t(A10Dx2) T+11 ns

#SDCEx delay time (1) t(CEDx2)n T+11 ns

#SDCEx delay time (2) t(CEDx2)p T+11 ns

#SDRAS signal delay time (1) t(RASDx2)n T+11 ns

#SDRAS signal delay time (2) t(RASDx2)p T+11 ns

#SDCAS signal delay time (1) t(CASDx2)n T+11 ns

#SDCAS signal delay time (2) t(CASDx2)p T+11 ns

HDQM, LDQM signal delay time (1) t(DQMDx2)n T+11 ns

HDQM, LDQM signal delay time (2) t(DQMDx2)p T+11 ns

SDCKE signal delay time (1) t(CKEDx2)n T+11 ns

SDCKE signal delay time (2) t(CKEDx2)p T+11 ns

#SDWE signal delay time (1) t(WEDx2)n T+11 ns

#SDWE signal delay time (2) t(WEDx2)p T+11 ns

Read data setup time t(RDSx2) (14) ns

Read data hold time t(RDHx2) (0) ns

Write data delay time t(WDDx2) 11 ns

Write data hold time t(WDHx2) T+11 ns

Note:"T" indicates one cycle time of the CPU clock.