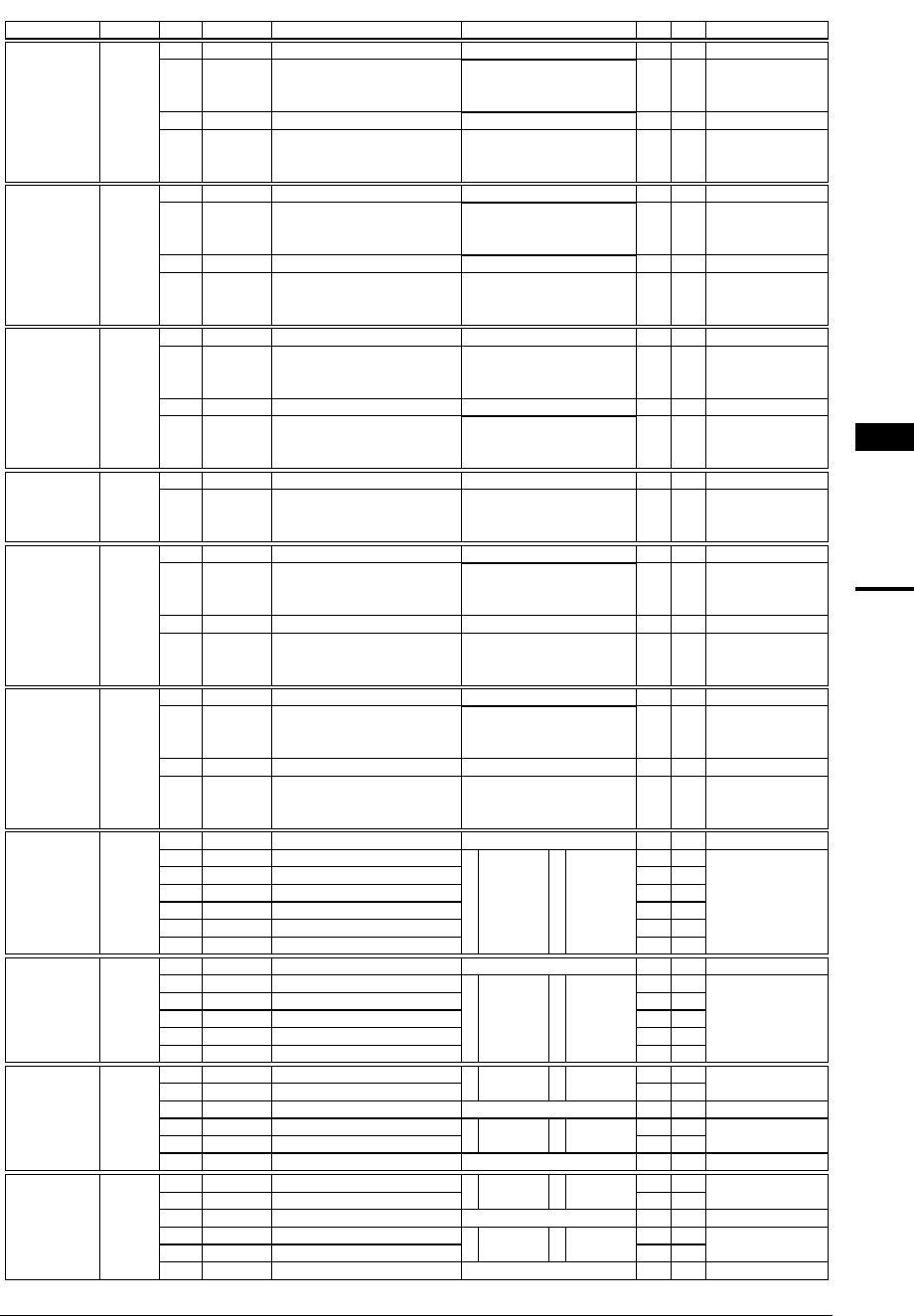

II CORE BLOCK: ITC (Interrupt Controller)

S1C33L03 FUNCTION PART EPSON B-II-5-13

A-1

B-II

ITC

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

0 to 7

0 to 7

–

–

P16T52

P16T51

P16T50

–

P16T42

P16T41

P16T40

D7

D6

D5

D4

D3

D2

D1

D0

reserved

16-bit timer 5 interrupt level

reserved

16-bit timer 4 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040268

(B)

16-bit timer 4/5

interrupt

priority register

–

0 to 7

0 to 7

–

–

PSI002

PSI001

PSI000

–

P8TM2

P8TM1

P8TM0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Serial interface Ch.0

interrupt level

reserved

8-bit timer 0–3 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040269

(B)

8-bit timer,

serial I/F Ch.0

interrupt

priority register

–

0 to 7

0 to 7

–

–

PAD2

PAD1

PAD0

–

PSI012

PSI011

PSI010

D7

D6

D5

D4

D3

D2

D1

D0

reserved

A/D converter interrupt level

reserved

Serial interface Ch.1

interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026A

(B)

Serial I/F Ch.1,

A/D interrupt

priority register

–

0 to 7

–

PCTM2

PCTM1

PCTM0

D7–3

D2

D1

D0

reserved

Clock timer interrupt level

–

X

X

X

–

R/W

Writing 1 not allowed.004026B

(B)

Clock timer

interrupt

priority register

–

0 to 7

0 to 7

–

–

PP5L2

PP5L1

PP5L0

–

PP4L2

PP4L1

PP4L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 5 interrupt level

reserved

Port input 4 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026C

(B)

Port input 4/5

interrupt

priority register

–

0 to 7

0 to 7

–

–

PP7L2

PP7L1

PP7L0

–

PP6L2

PP6L1

PP6L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 7 interrupt level

reserved

Port input 6 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026D

(B)

Port input 6/7

interrupt

priority register

–

EK1

EK0

EP3

EP2

EP1

EP0

D7–6

D5

D4

D3

D2

D1

D0

reserved

Key input 1

Key input 0

Port input 3

Port input 2

Port input 1

Port input 0

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040270

(B)

1 Enabled 0 Disabled

Key input,

port input 0–3

interrupt

enable register

–

EIDMA

EHDM3

EHDM2

EHDM1

EHDM0

D7–5

D4

D3

D2

D1

D0

reserved

IDMA

High-speed DMA Ch.3

High-speed DMA Ch.2

High-speed DMA Ch.1

High-speed DMA Ch.0

– –

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.0040271

(B)

1 Enabled 0 Disabled

DMA interrupt

enable register

E16TC1

E16TU1

–

E16TC0

E16TU0

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 1 comparison A

16-bit timer 1 comparison B

reserved

16-bit timer 0 comparison A

16-bit timer 0 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040272

(B)

1 Enabled 0 Disabled

16-bit timer 0/1

interrupt

enable register

–

1 Enabled 0 Disabled

–

E16TC3

E16TU3

–

E16TC2

E16TU2

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 3 comparison A

16-bit timer 3 comparison B

reserved

16-bit timer 2 comparison A

16-bit timer 2 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040273

(B)

1 Enabled 0 Disabled

16-bit timer 2/3

interrupt

enable register

–

1 Enabled 0 Disabled

–