VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-4 EPSON S1C33L03 FUNCTION PART

Notes:•Because the SDRAM address bus pins differ in bit numbers from ordinary external address pin

names, care must be taken when connecting an SDRAM to the S1C33. (SDRAM address

SDA0 is output from the A1 pin, and SDA12 is output from the A13 pin.) Furthermore, the

SDA10 signal with a special function is assigned to the P33 pin, and not to the address bus

A11.

•If designated pins (e.g., CKE and DQM[1:0] pins) must be driven high before the SDRAM can

be powered on, add external pull-up resistors or use a separate power supply for the SDRAM.

•To prevent a malfunction, take measures against noise when designing the board patterns for

the SDRAM.

Table 2.2 lists several examples of SDRAM chip configurations. All of these examples use only one area of the

S1C33. If your design uses two areas, the same type of memory needs to be used in each area because SDRAM-

related settings are common to both areas.

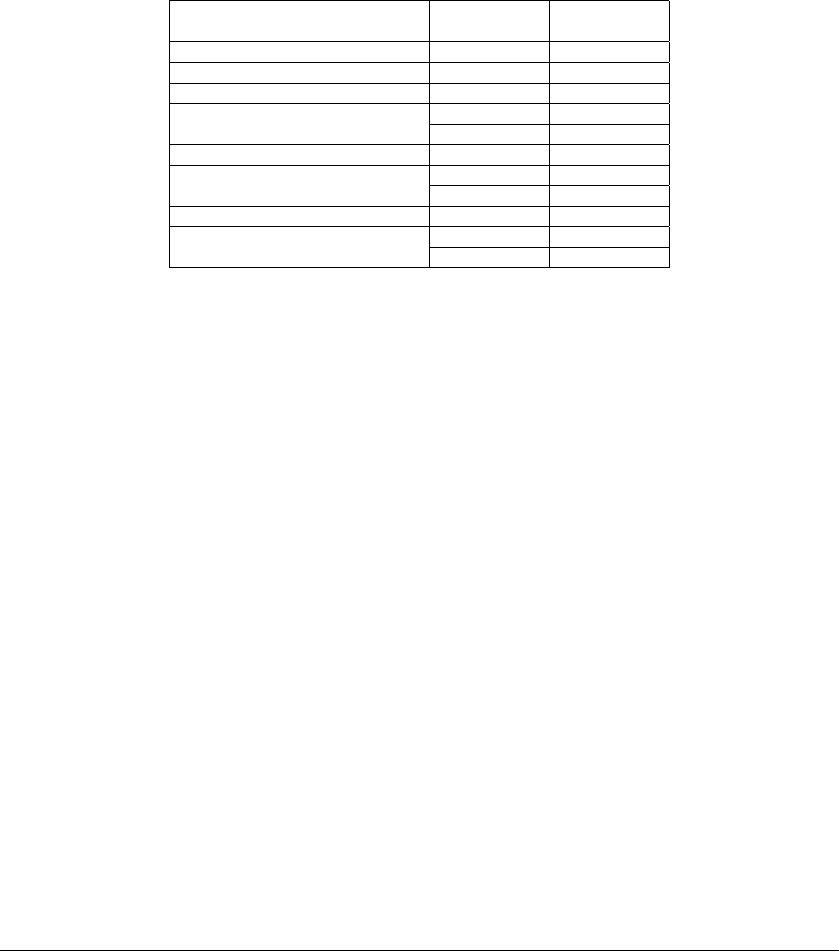

Table 2.2 Chip Configuration Example (when one area only is used)

SDRAM

Number of

devices

Memory size

256M (4M x 16 bits x 4 banks) 1 32M bytes

256M (8M x 8 bits x 4 banks) 1 32M bytes

128M (2M x 16 bits x 4 banks) 1 16M bytes

128M (4M x 8 bits x 4 banks) 1 16M bytes

232M bytes

64M (1M x 16 bits x 4 banks) 1 8M bytes

64M (2M x 8 bits x 4 banks) 1 8M bytes

216M bytes

16M (512 x 16 bits x 2 banks) 1 2M bytes

16M (1M x 8 bits x 2 banks) 1 2M bytes

24M bytes