VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

S1C33L03 FUNCTION PART EPSON B-VI-2-19

A-1

B-VI

SDRAM

Power-down Mode

The SDRAM controller supports three power-down modes for the S1C33 Core (HALT, HALT2, and SLEEP).

In HALT mode, the bus clock is not turned off. Therefore, this mode can be set at any time.

In HALT2 and SLEEP modes, the SDRAM’s auto-refresh function is disabled. Therefore, the SDRAM must be

placed in self-refresh mode before entering HALT2 or SLEEP mode, by following the procedure described below.

1. Set SDRSRF (D5/0x39FFC1) to "1" in order to enable the SDRAM’s self-refresh function.

2. Check to see that SDRSRM (D6/0x39FFCA) = "0" (i.e., SDRAM is being self-refreshed).

3. Execute the HALT or SLP instruction.

Because the OSC3 clock is required for the SDRAM controller to be able to operate, the SDRAM must also be

placed in self-refresh mode following the above procedure before switching the CPU clock to OSC1 or turning the

OSC3 clock off.

Note:Because the SDRAM is taken out of self-refresh mode when accessed, steps 2 and 3 of the above

procedure must be executed on other memory than SDRAMs.

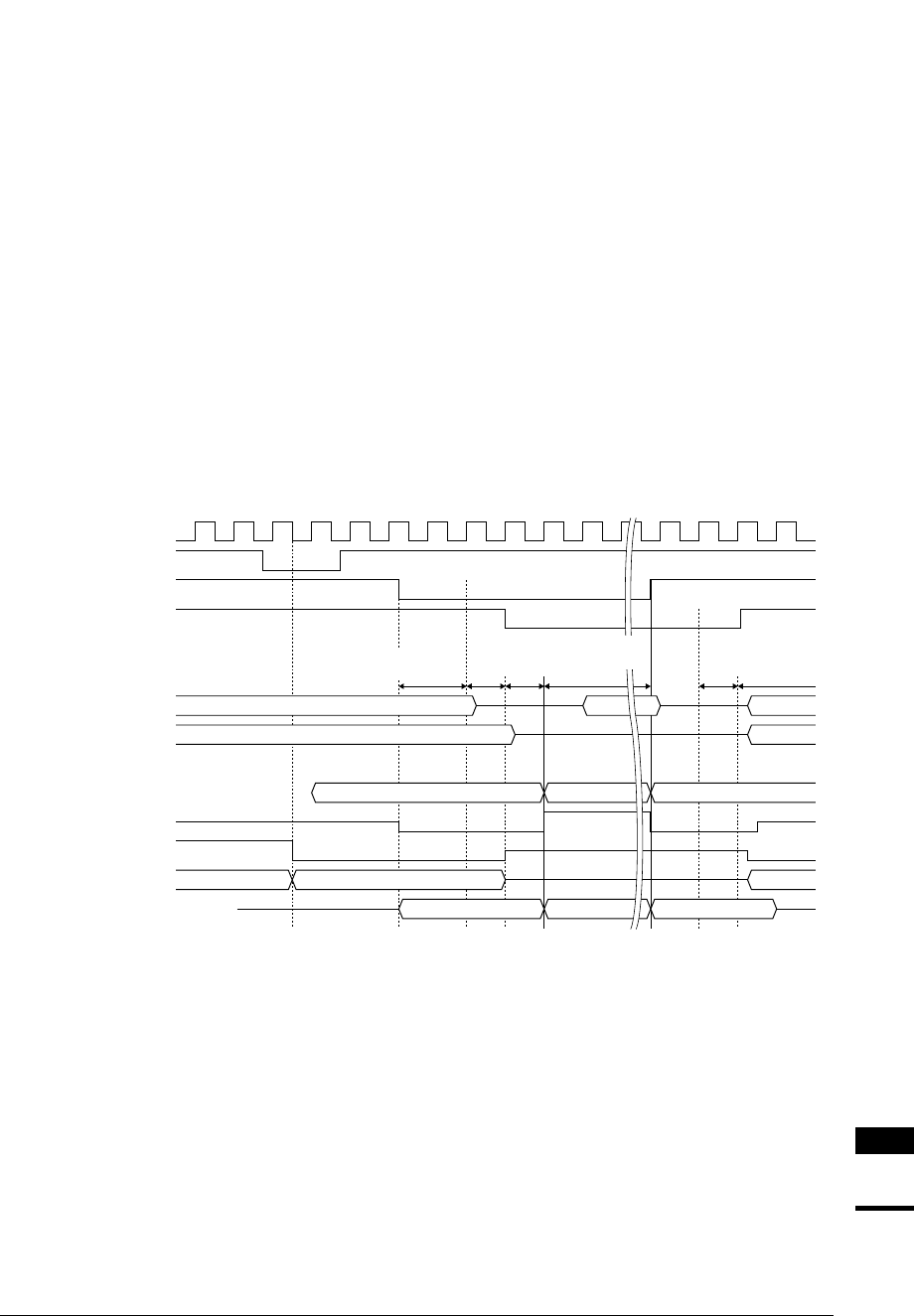

Bus Release Procedure

When the CPU releases the external bus, all of the SDRAM signal input/output pins, except for BCLK output when

SDRCLK = "1", are placed in the high-impedance state or set for input mode. As a result, another device acting as

the bus master gains control of the SDRAM.

The following illustrates a procedure where control of the SDRAM is switched.

BCLK

INTX (external device)

#BUSREQ

#BUSACK

D[15:0]

A[23:0], #RD, #WR

SDRAM status

CKE (external device)

SDCKE (S1C33)

SDRAM control (S1C33)

SDRAM control (external device)

1 cycle

Synchronization

Synchronization

S1C33 terminates

the current bus cycle.

S1C33 controls

bus cycles.

1 cycle

Hi-Z

Hi-Z

Hi-Z

Hi-ZHi-Z

Hi-Z

Hi-Z

1 cycle

CMD Self refresh

Self refresh CMD Self refresh

Self refresh CMD Self refresh

Self refresh

The external bus

master controls

bus cycles.

Figure 2.17 Bus Release Procedure