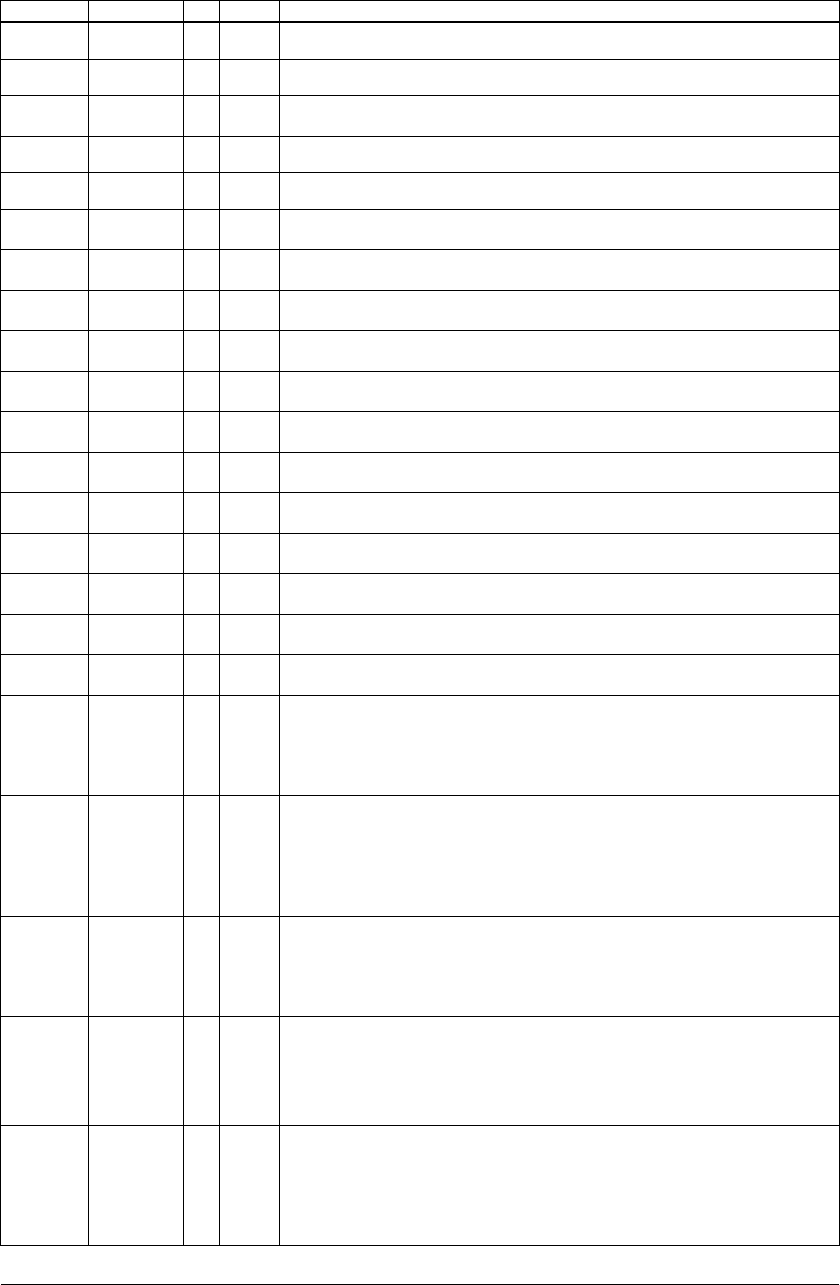

I OUTLINE: LIST OF PINS

B-I-3-4 EPSON S1C33L03 FUNCTION PART

Table 3.3 List of Pins for Internal Peripheral Circuits

Pin name Pin No. I/O Pull-up Function

K50

#DMAREQ0

41 I Pull-up K50: Input port when CFK50(D0/0x402C0) = "0" (default)

#DMAREQ0: HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1"

K51

#DMAREQ1

40 I Pull-up K51: Input port when CFK51(D1/0x402C0) = "0" (default)

#DMAREQ1: HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1"

K52

#ADTRG

39 I Pull-up K52: Input port when CFK52(D2/0x402C0) = "0" (default)

#ADTRG: A/D converter trigger input when CFK52(D2/0x402C0) = "1"

K53

#DMAREQ2

38 I Pull-up K53: Input port when CFK53(D3/0x402C0) = "0" (default)

#DMAREQ2: HSDMA Ch. 2 request input when CFK53(D3/0x402C0) = "1"

K54

#DMAREQ3

37 I Pull-up K54: Input port when CFK54(D4/0x402C0) = "0" (default)

#DMAREQ3: HSDMA Ch. 3 request input when CFK54(D4/0x402C0) = "1"

K60

AD0

35 I – K60: Input port when CFK60(D0/0x402C3) = "0" (default)

AD0: A/D converter Ch. 0 input when CFK60(D0/0x402C3) = "1"

K61

AD1

34 I – K61: Input port when CFK61(D1/0x402C3) = "0" (default)

AD1: A/D converter Ch. 1 input when CFK61(D1/0x402C3) = "1"

K62

AD2

33 I – K62: Input port when CFK62(D2/0x402C3) = "0" (default)

AD2: A/D converter Ch. 2 input when CFK62(D2/0x402C3) = "1"

K63

AD3

32 I – K63: Input port when CFK63(D3/0x402C3) = "0" (default)

AD3: A/D converter Ch. 3 input when CFK63(D3/0x402C3) = "1"

K64

AD4

31 I – K64: Input port when CFK64(D4/0x402C3) = "0" (default)

AD4: A/D converter Ch. 4 input when CFK64(D4/0x402C3) = "1"

K65

AD5

30 I – K65: Input port when CFK65(D5/0x402C3) = "0" (default)

AD5: A/D converter Ch. 5 input when CFK65(D5/0x402C3) = "1"

K66

AD6

29 I – K66: Input port when CFK66(D6/0x402C3) = "0" (default)

AD6: A/D converter Ch. 6 input when CFK66(D6/0x402C3) = "1"

K67

AD7

28 I – K67: Input port when CFK67(D7/0x402C3) = "0" (default)

AD7: A/D converter Ch. 7 input when CFK67(D7/0x402C3) = "1"

P00

SIN0

144 I/O – P00: I/O port when CFP00(D0/0x402D0) = "0" (default)

SIN0:Serial I/F Ch. 0 data input when CFP00(D0/0x402D0) = "1"

P01

SOUT0

143 I/O – P01: I/O port when CFP01(D1/0x402D0) = "0" (default)

SOUT0: Serial I/F Ch. 0 data output when CFP01(D1/0x402D0) = "1"

P02

#SCLK0

142 I/O – P02: I/O port when CFP02(D2/0x402D0) = "0" (default)

#SCLK0: Serial I/F Ch. 0 clock input/output when CFP02(D2/0x402D0) = "1"

P03

#SRDY0

141 I/O – P03: I/O port when CFP03(D3/0x402D0) = "0" (default)

#SRDY0: Serial I/F Ch. 0 ready signal input/output when CFP03(D3/0x402D0) = "1"

P04

SIN1

#DMAACK2

12 I/O – P04: I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0"

(default)

SIN1:Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and

CFEX4(D4/0x402DF) = "0"

#DMAACK2: HSDMA Ch. 2 acknowledge output when CFEX4(D4/0x402DF) = "1"

P05

SOUT1

#DMAEND2

11 I/O – P05: I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0"

(default)

SOUT1: Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

#DMAEND2: HSDMA Ch. 2 end-of-transfer signal output when

CFEX5(D5/0x402DF) = "1"

P06

#SCLK1

#DMAACK3

10 I/O – P06: I/O port when CFP06(D6/0x402D0) = "0" and CFEX6(D6/0x402DF) = "0"

(default)

#SCLK1: Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1" and

CFEX6(D6/0x402DF) = "0"

#DMAACK3: HSDMA Ch. 3 acknowledge output when CFEX6(D6/0x402DF) = "1"

P07

#SRDY1

#DMAEND3

9 I/O – P07: I/O port when CFP07(D7/0x402D0) = "0" and CFEX7(D7/0x402DF) = "0"

(default)

#SRDY1: Serial I/F Ch. 1 ready signal output when CFP07(D7/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

#DMAEND3: HSDMA Ch. 3 end-of-transfer signal output when

CFEX7(D7/0x402DF) = "1"

P10

EXCL0

T8UF0

DST0

122 I/O – P10: I/O port when CFP10(D0/0x402D4) = "0" and CFEX1(D1/0x402DF) = "0"

EXCL0: 16-bit timer 0 event counter input when CFP10(D0/0x402D4) = "1",

IOC10(D0/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"

T8UF0: 8-bit timer 0 output when CFP10(D0/0x402D4) = "1", IOC10(D0/0x402D6)

= "1" and CFEX1(D1/0x402DF) = "0"

DST0:DST0 signal output when CFEX1(D1/0x402DF) = "1" (default)