VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-2 EPSON S1C33L03 FUNCTION PART

I/O Pins and Connection

I/O Pins

Table 2.1 lists the pins used for the SDRAM interface.

Table 2.1 I/O Pin List

Pin name I/O Function

A[13:12]/SDA[12:11],

A[10:1]/SDA[9:0]

OAddress bus

A[15:14]/SDBA[1:0] O SDRAM bank select signals

D[15:0] I/O Data bus (D0–D15)

#CE8/#RAS1/#CE14/#RAS3/#SDCE1 O Area 8/14 chip enable / DRAM Row strobe / SDRAM chip enable 1

#CE7/#RAS0/#CE13/#RAS2/#SDCE0 O Area 7/13 chip enable / DRAM Row strobe / SDRAM chip enable 0

#HCAS/#SDCAS O DRAM column address strobe (High-byte) / SDRAM column address

strobe

#LCAS/#SDRAS O DRAM column address strobe (Low-byte) / SDRAM row address strobe

BCLK/SDCLK O Bus clock output / SDRAM operating clock

P20/#DRD/SDCKE I/O I/O port / DRAM read / SDRAM clock enable

P21/#DWE/#GAAS/#SDWE I/O I/O port / DRAM write (Low-byte) / Area address strobe output for GA /

SDRAM write

P33/#DMAACK1/SIN3/SDA10 I/O I/O port / HSDMA Ch. 1 acknowledge output / Serial I/F Ch. 3 data input /

SDRAM address bus 10

P32/#DMAACK0/#SRDY3/HDQM I/O I/O port / HSDMA Ch. 0 acknowledge output / Serial I/F Ch. 3 ready signal

output / SDRAM data (High-byte) input/output mask signal output

P15/EXCL4/#DMAEND0/#SCLK3/

LDQM

I/O I/O port / 16-bit timer 4 event counter input / HSDMA Ch. 0 end-of-transfer

signal output / Serial I/F Ch. 3 clock input/output / SDRAM data (Low-byte)

input/output mask signal output

Connection Examples

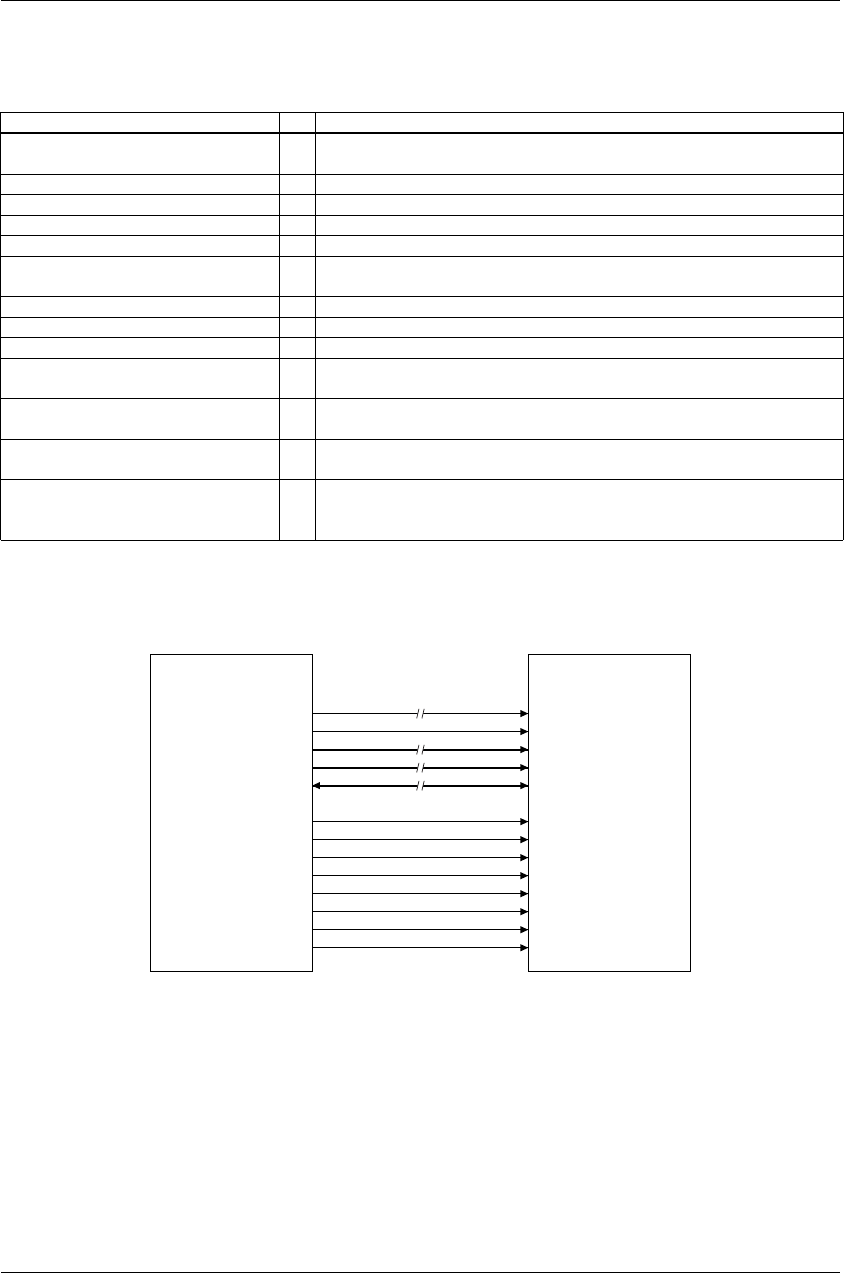

Figures 2.2 and 2.3 show examples of how to connect 16-bit SDRAMs to the S1C33. Figure 2.4 shows an example

of how to connect an 8-bit SDRAM to the S1C33.

SDA[12:11](A[13:12])

SDA10(P33)

SDA[9:0](A[10:1])

SDBA[1:0](A[15:14])

D[15:0]

BCLK

SDCKE(P20)

#SDCE0/1(#CE7/8)

#SDCAS(#HCAS)

#SDRAS(#LCAS)

#SDWE(P21)

HDQM(P32)

LDQM(P15)

S1C33

A[12:11]

A10

A[9:0]

BA[1:0]

DQ[15:0]

CLK

CKE

#CS

#CAS

#RAS

#WE

DQMU

DQML

256M SDRAM

(4M x 16 bits x 4 banks)

Figure 2.2 Connecting a 16-bit SDRAM (32MB)