III PERIPHERAL BLOCK: SERIAL INTERFACE

B-III-8-16 EPSON S1C33L03 FUNCTION PART

Setting the data format

In the asynchronous mode, the data length is 7 or 8 bits as determined by the transfer mode set. The start bit is

fixed at 1.

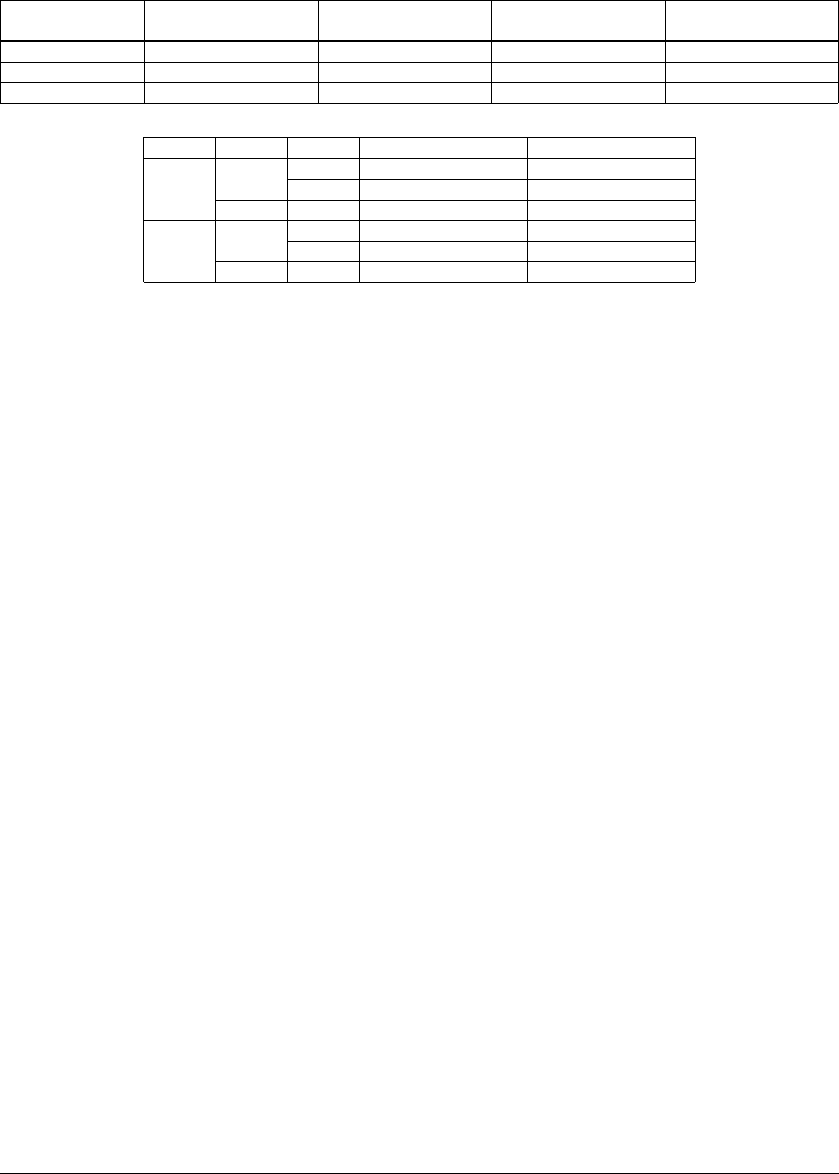

The stop and parity bits can be set as shown in the Table 8.5 using the following control bits:

Table 8.5 Serial I/F Control Bits

Ch.0 (Serial I/F Ch.0

control register)

Ch.1 (Serial I/F Ch.1

control register)

Ch.2 (Serial I/F Ch.2

control register)

Ch.3 (Serial I/F Ch.3

control register)

Stop-bit selection STPB0(D3/0x401E3) STPB1(D3/0x401E8) STPB2(D3/0x401F3) STPB3(D3/0x401F8)

Parity enable EPR0(D5/0x401E3) EPR1(D5/0x401E8) EPR2(D5/0x401F3) EPR3(D5/0x401F8)

Parity-mode selection PMD0(D4/0x401E3) PMD1(D4/0x401E8) PMD2(D4/0x401F3) PMD3(D4/0x401F8)

Table 8.6 Stop Bit and Parity Bit Settings

STPBx EPRx PMDx Stop bit Parity bit

111 2 bits Odd

02 bits Even

0 ∗ 2 bits None

011 1 bit Odd

01 bit Even

0 ∗ 1 bit Non

∗ Setting PMDx is invalid when EPRx = "0".

Note: These bits become indeterminate at initial reset, so be sure to initialize them in the software.

Control and Operation of Asynchronous Transfer

Transmit control

(1) Enabling transmit operation

Use the transmit-enable bit TXENx for transmit control.

Ch.0 transmit-enable: TXEN0 (D7) / Serial I/F Ch.0 control register (0x401E3)

Ch.1 transmit-enable: TXEN1 (D7) / Serial I/F Ch.1 control register (0x401E8)

Ch.2 transmit-enable: TXEN2 (D7) / Serial I/F Ch.2 control register (0x401F3)

Ch.3 transmit-enable: TXEN3 (D7) / Serial I/F Ch.3 control register (0x401F8)

When transmit is enabled by writing "1" to this bit, the clock input to the shift register is enabled (ready for

input), thus allowing data to be transmitted.

Transmit is disabled by writing "0" to TXENx.

Note: Do not set TXENx to "0" during a transmit operation.

(2) Transmit procedure

The serial interface has a transmit shift register and a transmit data register (transmit data buffer) that are

provided independently of those used for receive operations.

Ch.0 transmit data: TXD0[7:0] (D[7:0]) / Serial I/F Ch.0 transmit data register (0x401E0)

Ch.1 transmit data: TXD1[7:0] (D[7:0]) / Serial I/F Ch.1 transmit data register (0x401E5)

Ch.2 transmit data: TXD2[7:0] (D[7:0]) / Serial I/F Ch.2 transmit data register (0x401F0)

Ch.3 transmit data: TXD3[7:0] (D[7:0]) / Serial I/F Ch.3 transmit data register (0x401F5)

The serial interface starts a transmit operation by writing data to this register. In the 7-bit asynchronous mode,

bit 7 (MSB) in each register is ignored.

The serial interface also contains a status bit to indicate the status of the transmit data register.

Ch.0 transmit data buffer empty: TDBE0 (D1) / Serial I/F Ch.0 status register (0x401E2)

Ch.1 transmit data buffer empty: TDBE1 (D1) / Serial I/F Ch.1 status register (0x401E7)

Ch.2 transmit data buffer empty: TDBE2 (D1) / Serial I/F Ch.2 status register (0x401F2)

Ch.3 transmit data buffer empty: TDBE3 (D1) / Serial I/F Ch.3 status register (0x401F7)

This bit is reset to "0" by writing data to the transmit data register, and set back to "1" (buffer empty) when

the data is transferred to the shift register. The transfer begins when the serial interface starts sending the start

bit.