III PERIPHERAL BLOCK: SERIAL INTERFACE

B-III-8-24 EPSON S1C33L03 FUNCTION PART

Serial Interface Interrupts and DMA

The serial interface can generate the following three types of interrupts in each channel:

• Transmit-buffer empty interrupt

• Receive-buffer full interrupt

• Receive-error interrupt

Transmit-buffer empty interrupt factor

This interrupt factor occurs when the transmit data set in the transmit data register is transferred to the shift

register, in which case the interrupt factor flag FSTXx is set to "1". At this time, if the interrupt conditions set

using the interrupt control register are met, an interrupt to the CPU is generated.

Occurrence of this interrupt factor indicates that the next transmit data can be written to the transmit data

register.

This interrupt factor can also be used to invoke IDMA, enabling transmit data to be written to the register by

means of a DMA transfer.

Receive-completion interrupt

This interrupt factor occurs when a receive operation is completed and the receive data taken into the shift

register is transferred to the receive data register, in which case the interrupt factor flag FSRXx is set to "1".

At this time, if the interrupt conditions set using the interrupt control register are met, an interrupt to the CPU

is generated. Occurrence of this interrupt factor indicates that the received data can be read out.

This interrupt factor can also be used to invoke IDMA, enabling the received data to be written into specified

memory locations by means of a DMA transfer.

Receive-error interrupt

This interrupt factor occurs when a parity, framing, or overrun error is detected during data reception, in

which case the interrupt factor flag FSERRx is set to "1". At this time, if the interrupt conditions set using the

interrupt control register are met, an interrupt to the CPU is generated.

Since all three types of errors generate the same interrupt factor, check the error flags PERx (parity error),

OERx (overrun error), and FERx (framing error) to identify the type of error that has occurred. In the clock-

synchronized mode, parity and framing errors do not occur.

Note: If a receive error (parity or framing error) occurs, the receive-error interrupt and receive-buffer full

interrupt factors occur simultaneously. However, since the receive-error interrupt has priority over

the receive-buffer full interrupt, the receive-error interrupt is processed first. It is therefore

necessary for the receive-buffer full interrupt factor flag be cleared through the use of the receive-

error interrupt processing routine.

Control registers of the interrupt controller

•Ch.0 and Ch.1

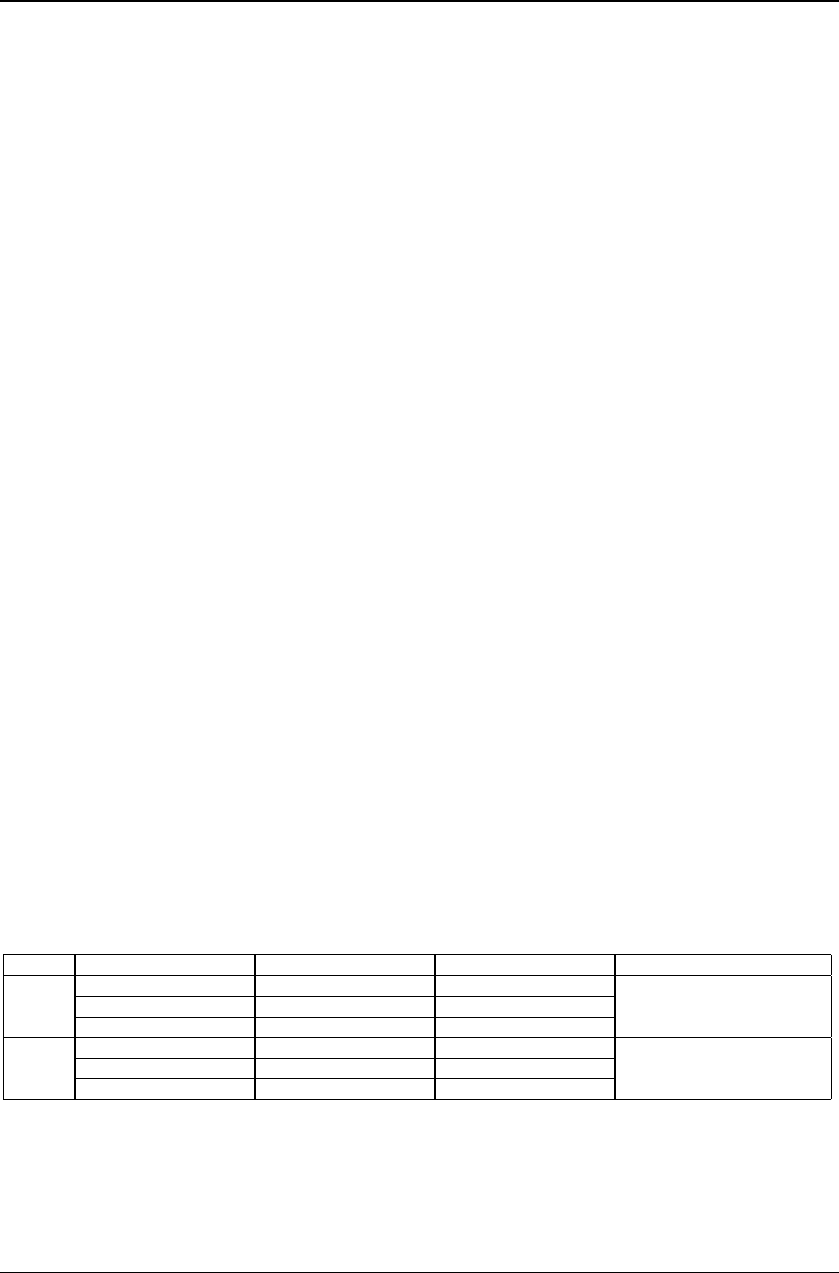

Table 8.9 shows the interrupt controller's control registers provided for each interrupt source (channel).

Table 8.9 Control Register of Interrupt Controller

Channel Interrupt factor Interrupt factor flag Interrupt enable register Interrupt priority register

Ch.0 Receive-error interrupt FSERR0(D0/0x40286) ESERR0(D0/0x40276) PSIO0[2:0](D[6:4]/0x40269)

Receive-buffer full FSRX0(D1/0x40286) ESRX0(D1/0x40276)

Transmit-buffer empty FSTX0(D2/0x40286) ESTX0(D2/0x40276)

Ch.1 Receive-error interrupt FSERR1(D3/0x40286) ESERR1(D3/0x40276) PSIO1[2:0](D[2:0]/0x4026A)

Receive-buffer full FSRX1(D4/0x40286) ESRX1(D4/0x40276)

Transmit-buffer empty FSTX1(D5/0x40286) ESTX1(D5/0x40276)

When the interrupt factor described above occurs, the corresponding interrupt factor flag is set to "1". If the

interrupt enable register bit for that interrupt factor has been set to "1", an interrupt request is generated.

Interrupts caused by an interrupt factor can be disabled by leaving the interrupt enable register bit for that

factor set to "0". The interrupt factor flag is set to "1" whenever interrupt conditions are met, regardless of the

setting of the interrupt enable register (even if it is set to "0").