8 ELECTRICAL CHARACTERISTICS

S1C33L03 PRODUCT PART EPSON A-101

A-1

A-8

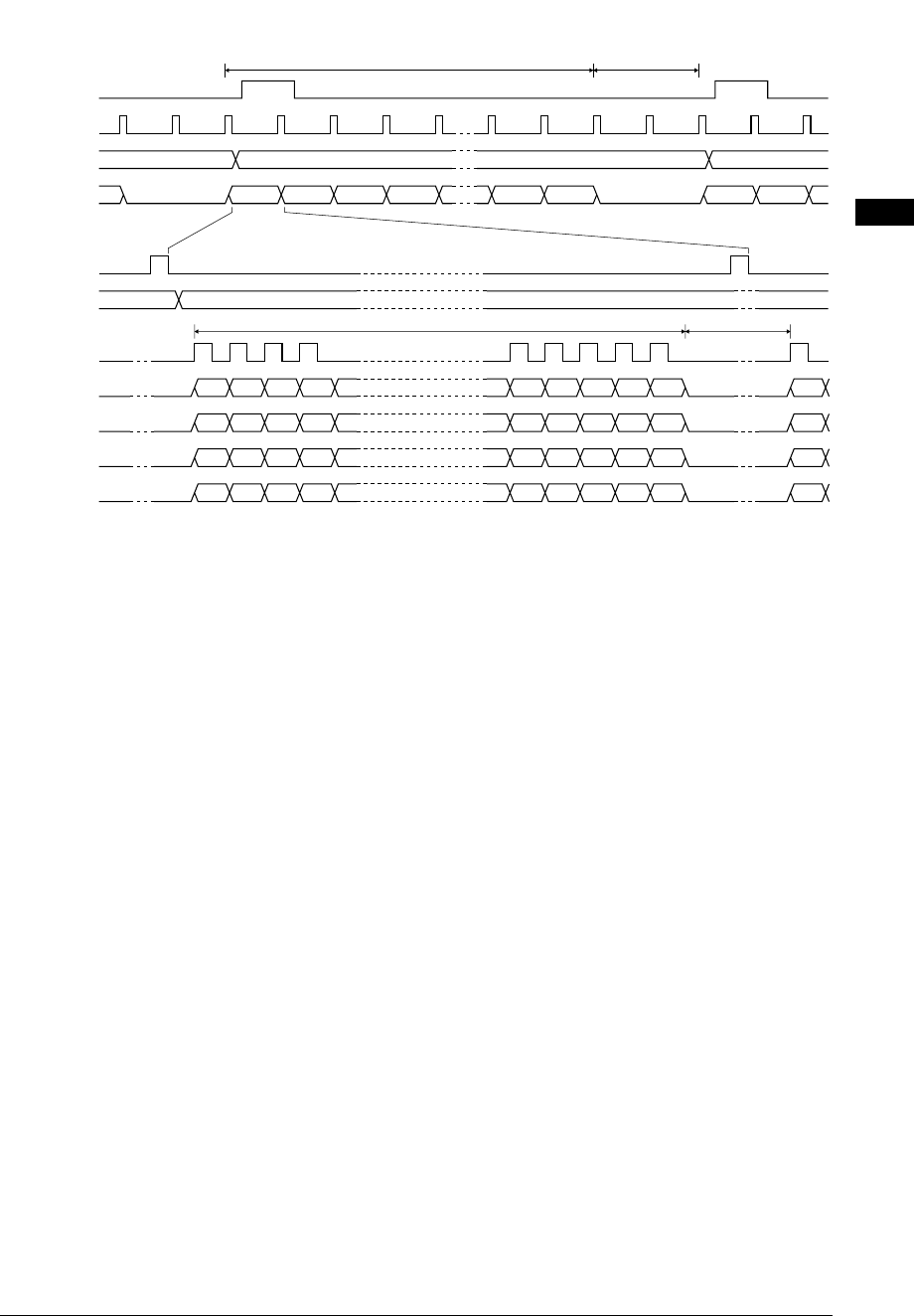

4-bit single color panel timing

FPFRAME

FPLINE

DRDY (MOD)

FPDAT[7:4]

VDP VNDP

FPLINE

DRDY (MOD)

FPSHIFT

FPDAT7

FPDAT6

FPDAT5

FPDAT4

Line 1

1-R1 1-G2

1-B319

1-G1 1-B2

1-R320

1-B1 1-R3

1-G320

1-R2 1-G3

1-B3

1-R4

1-G4

1-B4

1-B320

Line 2 Line 3 Line 1 Line 2Line 4 Line 239 Line 240

HDP HNDP

∗ Diagram drawn with 2 FPLINE vertical blank period

Example timing for a 320 × 240 panel

VDP = Vertical Display Period = LDVSIZE[9:0] + 1 (lines)

LDVSIZE[9:0] (0x39FFE5, D[1:0]/0x39FFE6)

VNDP = Vertical Non-Display Period = VNDP[5:0] (lines)

VNDP[5:0] (D[5:0]/0x39FFEA)

HDP = Horizontal Display Period = (LDHSIZE[5:0] + 1) × 16 (Ts)

LDHSIZE[5:0] (D[5:0]/0x39FFE4)

HNDP = Horizontal Non-Display Period = (HNDP[4:0] + 4) × 8 (Ts)

HNDP[4:0] (D[4:0]/0x39FFE7)