II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-30 EPSON S1C33L03 FUNCTION PART

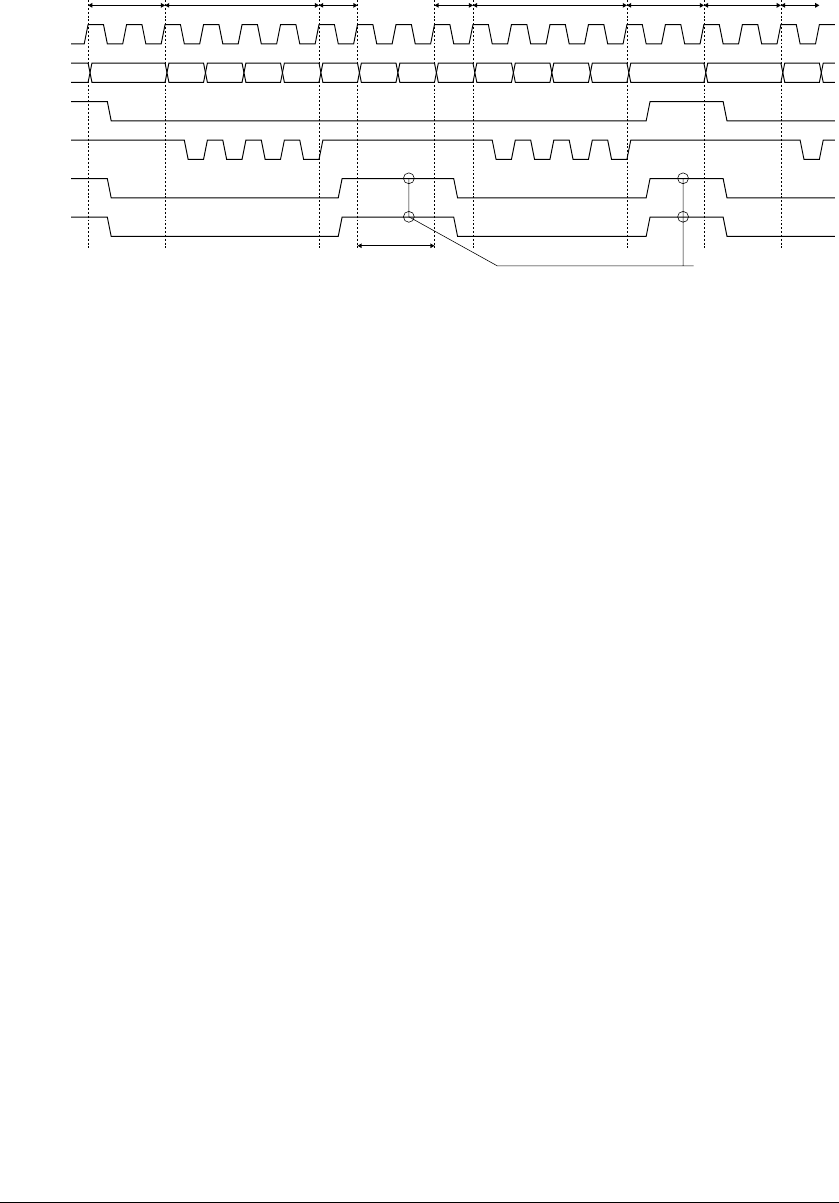

Operation in successive RAS mode

Example: RAS: 2 cycles; CAS: 1 cycle; Precharge: 2 cycles

BCLK

A[11:0]

#RASx

#HCAS/

#LCAS

#DRD

#DWE

RAS

cycle

Accsess to other

device than DRAM

Not asserted for areas

other than DRAM

Precharge

cycle

Deassert

cycle

Assert

cycle

CAS cycles

in page mode

RAS

cycle

CAS

cycles

CAS cycles

in page mode

(1) (2) (3) (4)

Figure 4.35 Operation in Successive RAS Mode

(1) When accessing the DRAM area, an ordinary RAS cycle is executed first.

(2) If access to the same DRAM is suspended during a page mode, #RASx remains asserted while some other

device is accessed. In this case, a cycle to temporarily deassert #DRD/#DWE is inserted before accessing the

other device.

(3) If access to the same page in the same DRAM area as in (1) is requested after (2), #DRD/#DWE is asserted

back again to restart the page mode.

(4) A precharge cycle is executed when one of the following conditions that cause the page mode to suspend is

encountered:

• access to different DRAM is requested;

• access to a different page in the same DRAM area is requested;

• access to some other device than DRAM is requested;

• CAS-before-RAS refresh is requested; and

• relinquishing of bus control is requested by an external bus master.

Note: When using the successive RAS mode, always be sure to use #DRD for the read signal and

#DWE for the low-byte write signal.