III PERIPHERAL BLOCK: WATCHDOG TIMER

S1C33L03 FUNCTION PART EPSON B-III-5-1

A-1

B-III

WDT

III-5 WAT C H D OG TIMER

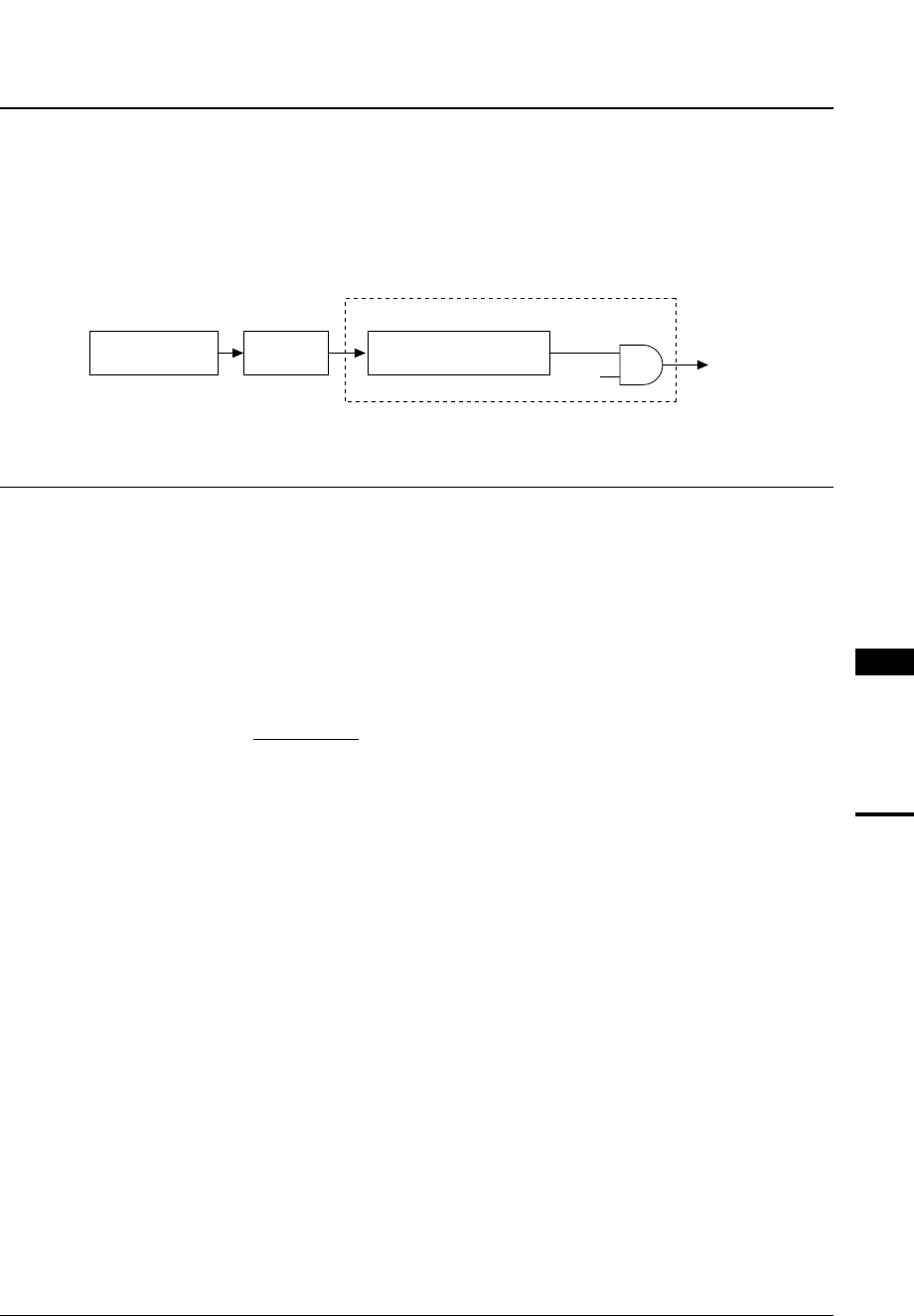

Configuration of Watchdog Timer

The Peripheral Block incorporates a watchdog timer function to detect the CPU's crash.

This function is implemented through the use of the 16-bit programmable timer 0. When this function is enabled,

an NMI (nonmaskable interrupt) is generated by the comparison B signal from the 16-bit programmable timer 0

(generating intervals can be set through the use of software). The 16-bit programmable timer 0 set in the software

so as not to generate the NMI, making it possible to detect a program crash that may not pass through this

processing routine.

Figure 5.1 shows the block diagram of the watchdog timer.

Clock generator

16-bit

programmable timer 0

Prescaler

NMI

Watchdog timer

EWD

Figure 5.1 Watchdog Timer Block Diagram

Control of Watchdog Timer

Setting the operating clock and NMI generating interval

The watchdog timer is operated by the prescaler's output clock. Therefore, the watchdog timer function

cannot be used when the prescaler is inactive.

The NMI is generated every time the 16-bit programmable timer 0 is reset by the comparison B setting.

Therefore, this interval is determined by the prescaler's P16TS0[2:0] (D[2:0]) / 16-bit timer 0 clock control

register (0x40147), and the comparison data B set in CR0B[15:0] (D[F:0]) / 16-bit timer 0 comparison

register B (0x48182).

The NMI generating interval is calculated using the following equation:

NMI generating interval =

CR0B + 1

[sec.]

fPSCIN × pdr

f

PSCIN:Prescaler input clock frequency [Hz]

pdr: Prescaler's division ratio set by the P16TS0 register (1/4096, 1/1024, 1/256, 1/64, 1/16, 1/4, 1/2, 1/1)

CR0B: Set value of the CR0B register (0 to 65,535)

For details on how to control the prescaler and the 16-bit programmable timer 0, refer to "Prescaler" and "16-

Bit Programmable Timers".

Setting the watchdog timer function

To use the watchdog timer function, enable the NMI that is generated by the comparison B signal from the

16-bit programmable timer 0. For this purpose, use EWD (D1) / Watchdog timer enable register (0x40171).

The NMI is enabled by writing "1" to EWD. At initial reset, EWD is set to "0", so generation of the NMI is

disabled.

To prevent an unwanted NMI from being generated by erroneous writing to EWD, this register is normally

write-protected. To write-enable EWD, write "1" to WRWD (D7) / Watchdog timer write-protect register

(0x40170). Only one writing to EWD is enabled in this way by the WRWD bit. When data is written to EWD

after it is write-enabled, the WRWD bit is reset back to "0", thus making EWD write-protected again.

For the 16-bit programmable timer 0, set an appropriate comparison B value to make it start operating.

If the watchdog timer function is not to be used, set EWD to "0" and do not change it.