III PERIPHERAL BLOCK: INPUT/OUTPUT PORTS

B-III-9-14 EPSON S1C33L03 FUNCTION PART

Key Input Interrupt

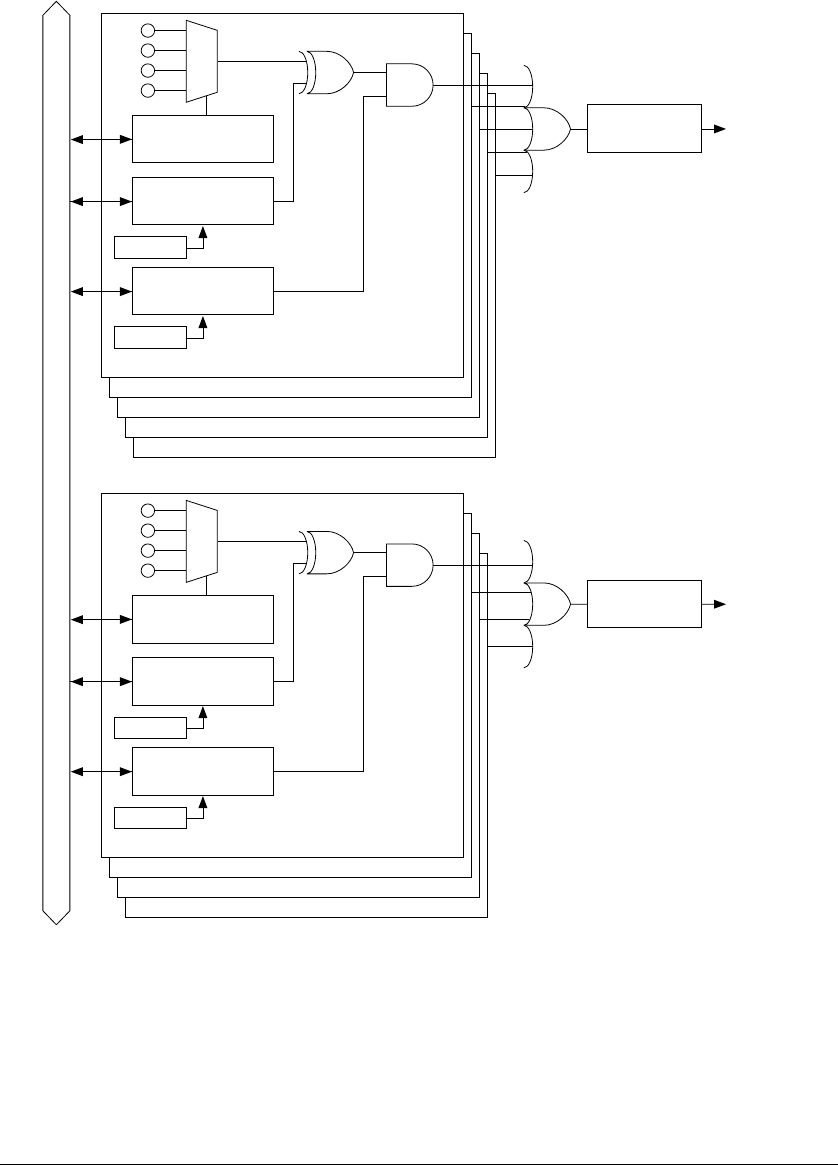

The key input interrupt circuit has two interrupt systems (FPK1 and FPK0) and a port group can be selected for

generating each interrupt factor.

The interrupt condition can also be set by software.

Figure 9.4 shows the configuration of the port input interrupt circuit.

Internal data bus

K54, K64, P04, P24

K53, K63, P03, P23

K52, K62, P02, P22

K50

K60

P00

P20

Input comparison

register SCPK0

Input mask

register SMPK0

Address

Address

K51, K61, P01, P21

K50, K60, P00, P20

Input port selection

SPPK0

FPK0

Interrupt

request

Interrupt signal

generation

FPK0 system

K63, K67, P07, P27

K62, K66, P06, P26

K60

K64

P04

P24

Input comparison

register SCPK1

Input mask

register SMPK1

Address

Address

K61, K65, P05, P25

K60, K64, P04, P24

Input port selection

SPPK1

FPK1

Interrupt

request

Interrupt signal

generation

FPK1 system

Figure 9.4 Configuration of Key Input Interrupt Circuit