IV ANALOG BLOCK: A/D CONVERTER

S1C33L03 FUNCTION PART EPSON B-IV-2-13

A-1

B-IV

A/D

ST1–ST0: Sampling-time setup (D[1:0]) / A/D sampling register (0x40245)

Sets the analog input sampling time.

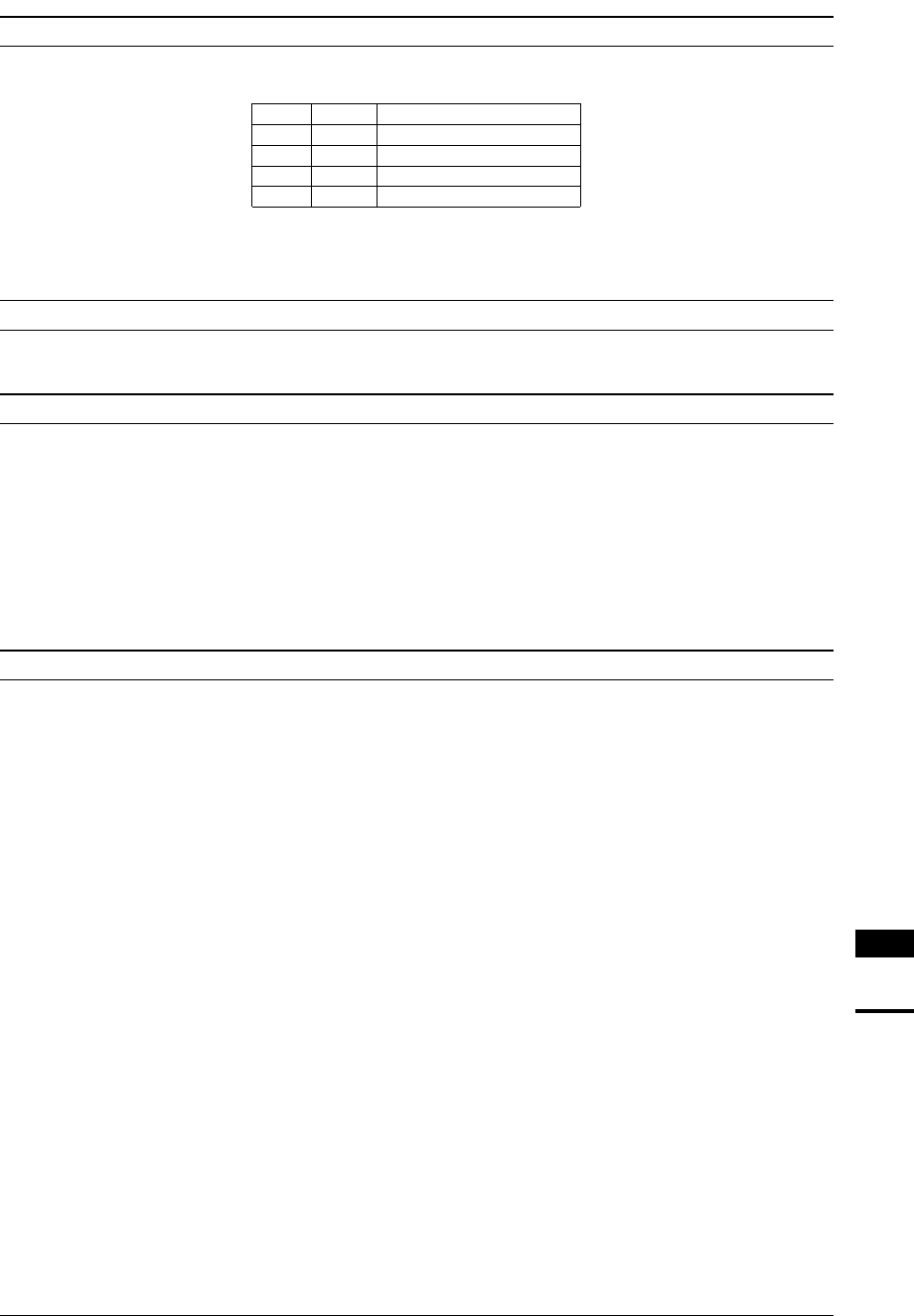

Table 2.8 Sampling Time

ST1 ST0 Sampling Time

11 9-clock period

10 7-clock period

01 5-clock period

00 3-clock period

The A/D converter input clock is used for counting.

At initial reset, ST is set to "11" (9-clock period).

To maintain the conversion accuracy, use ST as set by default (9-clock period).

PAD2–PAD0:

A/D converter interrupt level (D[6:4]) / Serial I/F Ch.1, A/D interrupt priority register (0x4026A)

Sets the priority level of the A/D-converter interrupt in the range of 0 to 7.

At initial reset, PAD becomes indeterminate.

EADE:

A/D converter interrupt enable (D0) / Port input 4–7, clock timer, A/D interrupt enable register (0x40277)

Enables or disables an interrupt to the CPU generated by the A/D converter.

Write "1": Interrupt enabled

Write "0": Interrupt disabled

Read: Valid

EADE is an interrupt enable bit to control the A/D converter interrupt.

When EADE is set to "1", the A/D converter interrupt is enabled. When EADE is set to "0", the A/D-converter

interrupt is disabled.

At initial reset, EADE is set to "0" (interrupt disabled).

FADE:

A/D converter interrupt factor flag (D0) / Port input 4–7, clock timer, A/D interrupt factor flag register (0x40287)

Indicates the status of an A/D-converter interrupt factor generated.

When read

Read "1": Interrupt factor has occurred

Read "0": No interrupt factor has occurred

When written using the reset-only method (default)

Write "1": Interrupt factor flag is reset

Write "0": Invalid

When written using the read/write method

Write "1": Interrupt flag is set

Write "0": Interrupt flag is reset

FADE is the interrupt factor flag of the A/D converter. It is set to "1" upon completion of A/D conversion in one

channel (i.e., when the conversion results are written into the ADD register).

At this time, if the following conditions are met, an interrupt to the CPU is generated:

1. The corresponding interrupt enable register bit is set to "1".

2. No other interrupt request of a higher priority has been generated.

3. The IE bit of the PSR is set to "1" (interrupts enabled).

4. The value set in the corresponding interrupt priority register is higher than the interrupt level (IL) of the CPU.

When using the interrupt factor of the A/D converter to request IDMA, note that even when the above conditions

are met, no interrupt request to the CPU is generated for the interrupt factor that has occurred. If interrupts are

enabled at the setting of IDMA, an interrupt is generated under the above conditions after the data transfer by

IDMA is completed.