III PERIPHERAL BLOCK: 16-BIT PROGRAMMABLE TIMERS

S1C33L03 FUNCTION PART EPSON B-III-4-1

A-1

B-III

16TM

III-4 16-BIT PROGRAMMABLE TIMERS

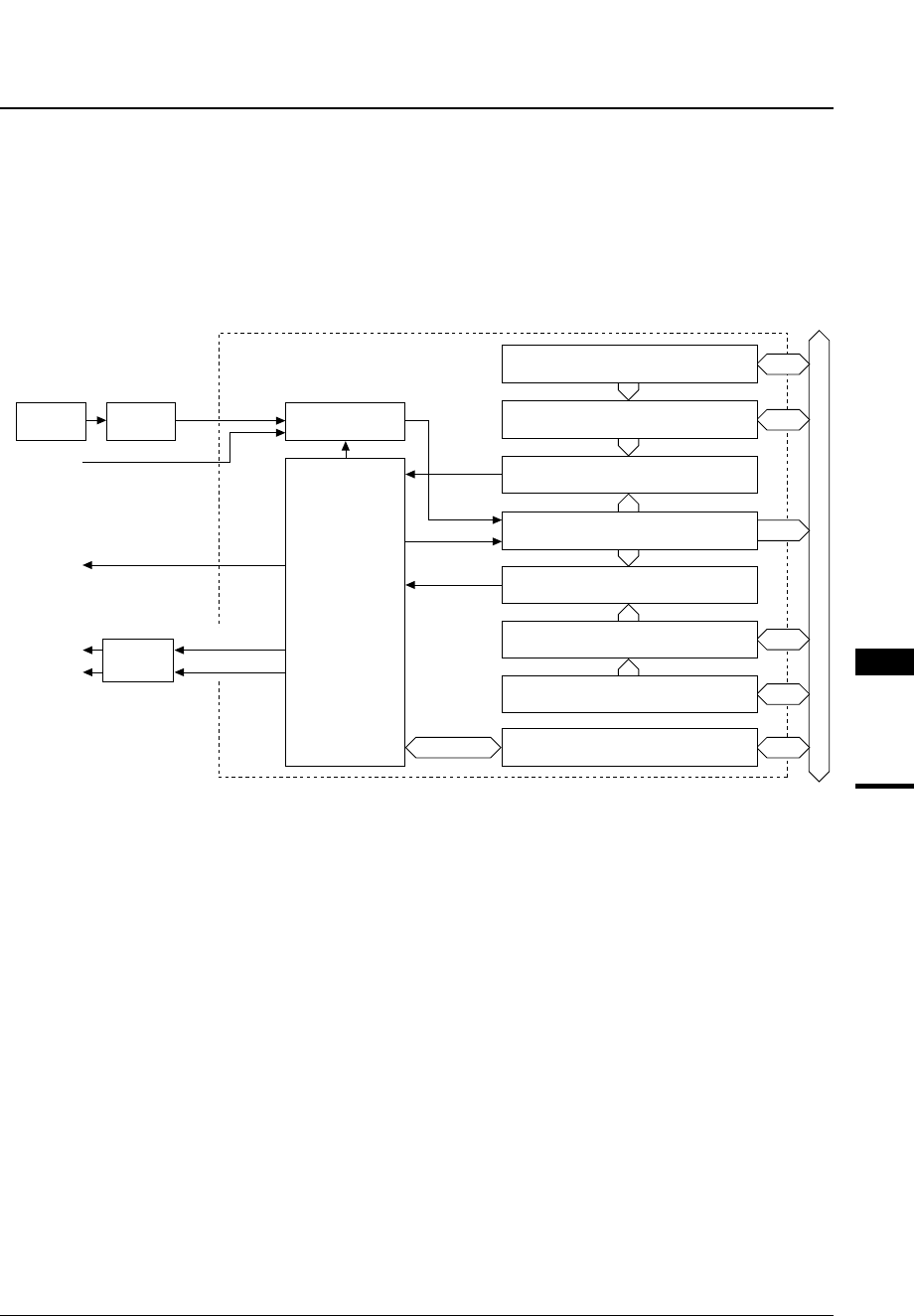

Configuration of 16-Bit Programmable Timer

The Peripheral Block contains six systems of 16-bit programmable timers (timers 0 to 5). They also have an event

counter function using an I/O port pin.

Note: On the following pages, each timer is identified as timer x (x = 0 to 5). The functions and control

register structures of 16-bit programmable timers 0 to 5 are the same. Control bit names are

assigned numerals "0" to "5" denoting timer numbers. Since explanations are common to all timers,

timer numbers are represented by "x" unless it is necessary to specify a timer number.

Figure 4.1 shows the structure of one channel of the 16-bit programmable timer.

Data bus

16-bit up counter (TCx)

16-bit comparison data register B (CRxB)

Comparison register B buffer (CRBxB)

16-bit comparison data register A (CRxA)

Comparison register A buffer (CRBxA)

Timer x control register

Control circuit

Clock select circuitPrescaler

Clock

generator

Comparator

Comparator

INCLx

Clock output

TMx

Comparison A

interrupt

Comparison B

interrupt

Comparison

match B

Comparison

match A

Comparison A

Comparison B

Timer x

Interrupt

controller

External clock

EXCLx

Figure 4.1 Structure of 16-Bit Programmable Timer

In each timer, a 16-bit up-counter (TCx), as well as two 16-bit comparison data registers (CRxA, CRxB) and their

buffers (CRBxA, CRBxB), are provided.

The 16-bit counter can be reset to "0" by software and counts up using the prescaler output clock or an external

signal input from the I/O port. The counter value can be read by software.

The comparison data registers A and B are used to store the data to be compared with the content of the up-counter.

This register can be directly read and written. Furthermore, comparison data can be set via the comparison register

buffer. In this case, the set value is loaded to the comparison data register when the counter is reset by the

comparison match B signal or software (by writing "1" to PRESETx bit). The software can select whether

comparison data is written to the comparison data register or the buffer.

When the counter value matches to the content of each comparison data register, the comparator outputs a signal

that controls the interrupt and the output signal. Thus the registers allow interrupt generating intervals and the

timer's output clock frequency and duty ratio to be programmed.