II CORE BLOCK: CLG (Clock Generator)

S1C33L03 FUNCTION PART EPSON B-II-6-7

A-1

B-II

CLG

CLKCHG: CPU operating clock switch (D2) / Power control register (0x40180)

Selects the CPU operating clock.

Write "1": OSC3 clock

Write "0": OSC1 clock

Read: Valid

The OSC3 clock is selected as the CPU operating clock by writing "1" to CLKCHG, and OSC1 is selected by

writing "0". The operating clock can be switched over in this way only when both the high-speed (OSC3) and low-

speed (OSC1) oscillation circuits are on. In addition, writing to CLKCHG is effective only when CLGP[7:0] is set

to "0b10010110". Immediately after the oscillation circuit has started oscillating, wait for the oscillation to stabilize

before switching over the CPU operating clock.

At initial reset, CLKCHG is set to "1" (OSC3 clock).

Note: This control bit is effective only when the low-speed (OSC1) oscillation circuit in the Peripheral

Block is used.

CLKDT1–CLKDT0: CPU operating frequency selection (D[7:6]) / Power control register (0x40180)

Select the CPU operating clock frequency.

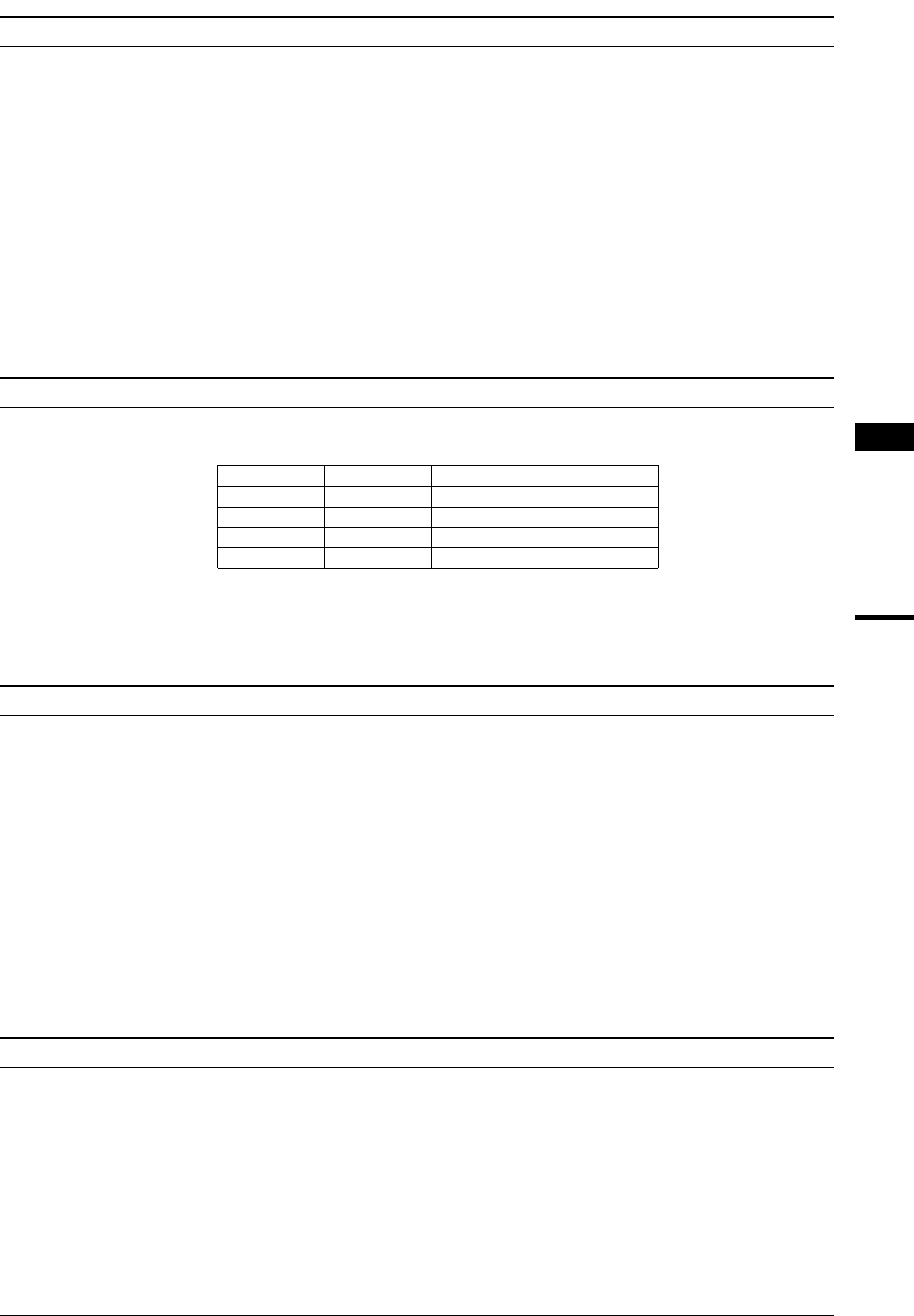

Table 6.5 Setting of CPU Operating Clock

CLKDT1 CLKDT0 Division ratio

11 fout/8

10 fout/4

01 fout/2

00 fout/1

fout: PLL output

This setting is effective when the CPU is operated using the high-speed (OSC3) clock and has no effect on the low-

speed (OSC1) clock. Writing to CLKDT[1:0] is allowed only when CLGP[7:0] is set to "0b10010110".

At initial reset, CLKDT is set to "0" (fout/1).

8T1ON: High-speed (OSC3) oscillation waiting function (D2) / Clock option register (0x40190)

Sets the function for waiting until the high-speed (OSC3) oscillation stabilizes after SLEEP mode is exited.

Write "1": Off

Write "0": On

Read: Valid

After SLEEP mode is exited, the high-speed (OSC3) oscillation waiting function is effective by writing "1" to

8T1ON. For this function to be used, the waiting time must be set in 8-bit programmable timer 1 to allow it to start

counting before entering SLEEP mode. After SLEEP mode is exited, the OSC3 clock is not supplied to the CPU

until 8-bit programmable timer 1 underflows. This function will not work when 8T1ON is set to "0".

The high-speed (OSC3) oscillation waiting function is effective only when SLEEP mode is exited.

Writing to 8T1ON is effective only when CLGP[7:0] is set to "0b10010110".

When writing to 8T1ON, always be sure to write "0" to the reserved bits at address 0x40190.

At initial reset, 8T1ON is set to "1" (Off).

HLT2OP: HALT clock option (D3) / Clock option register (0x40190)

Select a HALT condition (basic mode or HALT2 mode).

Write "1": HALT2 mode

Write "0": Basic mode

Read: Valid

When "1" is written to HLT2OP, the CPU will enter HALT2 mode when the HALT instruction is executed. When

"0" is written, the CPU will enter basic mode.

Writing to HLT2OP is allowed only when CLGP[7:0] is set to "0b10010110".

At initial reset, HLT2OP is set to "0" (basic mode).

The following shows the operating status in HALT mode (basic mode and HALT2 mode) and SLEEP mode.