VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-16 EPSON S1C33L03 FUNCTION PART

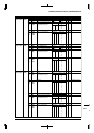

Figure 2.12 shows an example of a timing chart in cases where the row address is varied during burst read.

BCLK

Command

SDCKE

#SDCEx

#SDRAS

#SDCAS

#SDWE

SDBA[1:0]

SDA[10]

SDA[12:11, 9:0]

LDQM/HDQM

DQ[15:0]

ACTVNOP

H

NOP NOP NOPPRE NOP READ

BA BA

ROW1

D

(n)

D

(n+1)

D

(n+2)

D

(0)

D

(1)

D

(2)

tRCDtRP tRCD

tRAS

tRPCAS latency

= 2

CAS latency

= 2

ROW1 COLn

BA

ACTV NOPPRE NOP READ

BA BA

ROW2

ROW2 COL0

BA

Figure 2.12 Changing Row Address During Burst Read

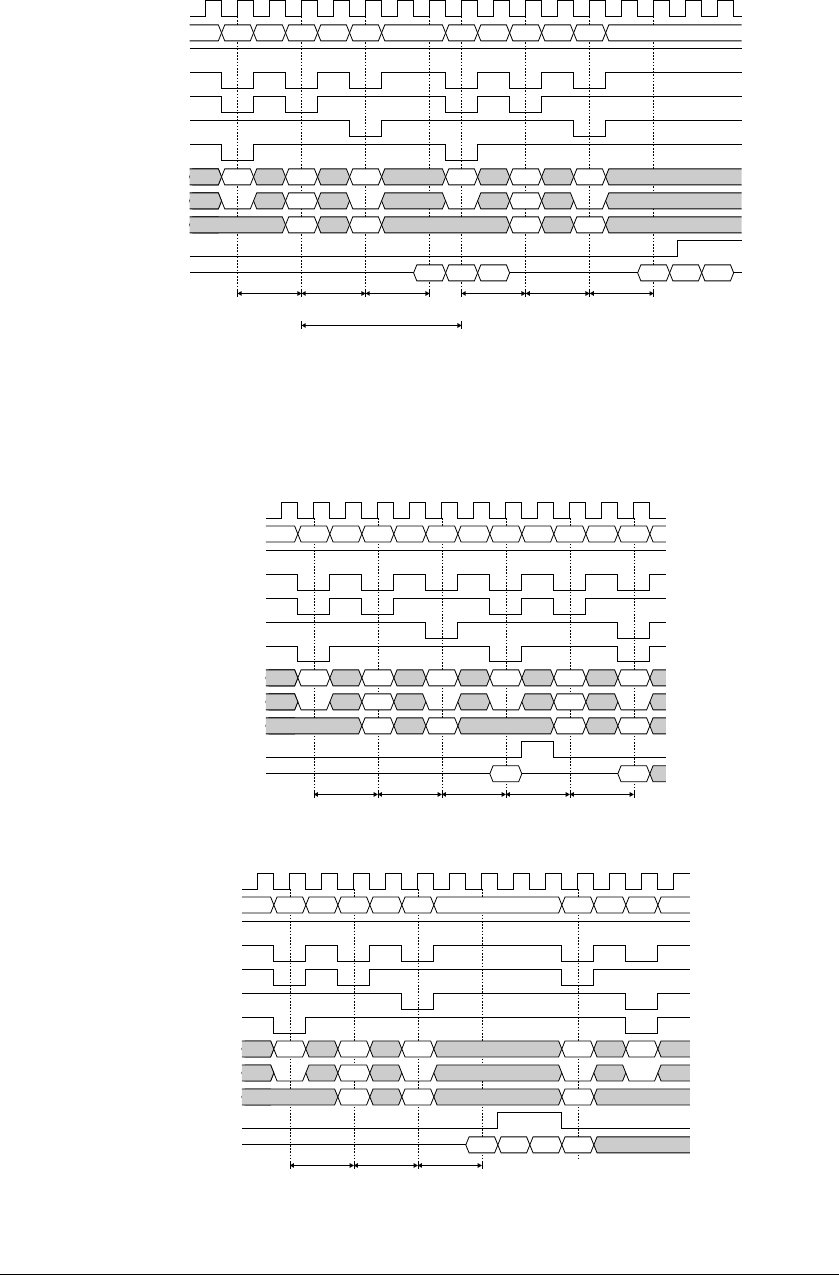

Single Read/Single Write

If the burst length is set to "1" (SDRBL[1:0] = "00"), the SDRAM controller reads data from the SDRAM in a

single operation.

When writing to the SDRAM, data are always written in a single operation, no matter what burst length is selected.

BCLK

Command

SDCKE

#SDCEx

#SDRAS

#SDCAS

#SDWE

SDBA[1:0]

SDA[10]

SDA[12:11, 9:0]

LDQM/HDQM

DQ[15:0]

ACTVNOP

H

NOP NOPPRE NOP READ

BA1 BA1

ROW1

D(1)

tRCDtRP tRCDtRPCAS latency

= 2

ROW1 COL1

BA1

ACTV NOPPRE NOP

BA2 BA2

ROW2

ROW2 COL2

BA2

D(2)

WRIT

Figure 2.13 Single Read to Single Write (different page)

BCLK

Command

SDCKE

#SDCEx

#SDRAS

#SDCAS

#SDWE

SDBA[1:0]

SDA[10]

SDA[12:11, 9:0]

LDQM/HDQM

DQ[15:0]

ACTVNOP

H

NOP NOP NOPPRE NOP READ

BA BA

ROW1

D(n) D(n+1) D(n+2) D(m)

tRCDtRP CAS latency

= 2

ROW1 COLn

BA

WRIT NOP PRE

BA

COLm

BA

Figure 2.14 Burst Read to Single Write (same page)