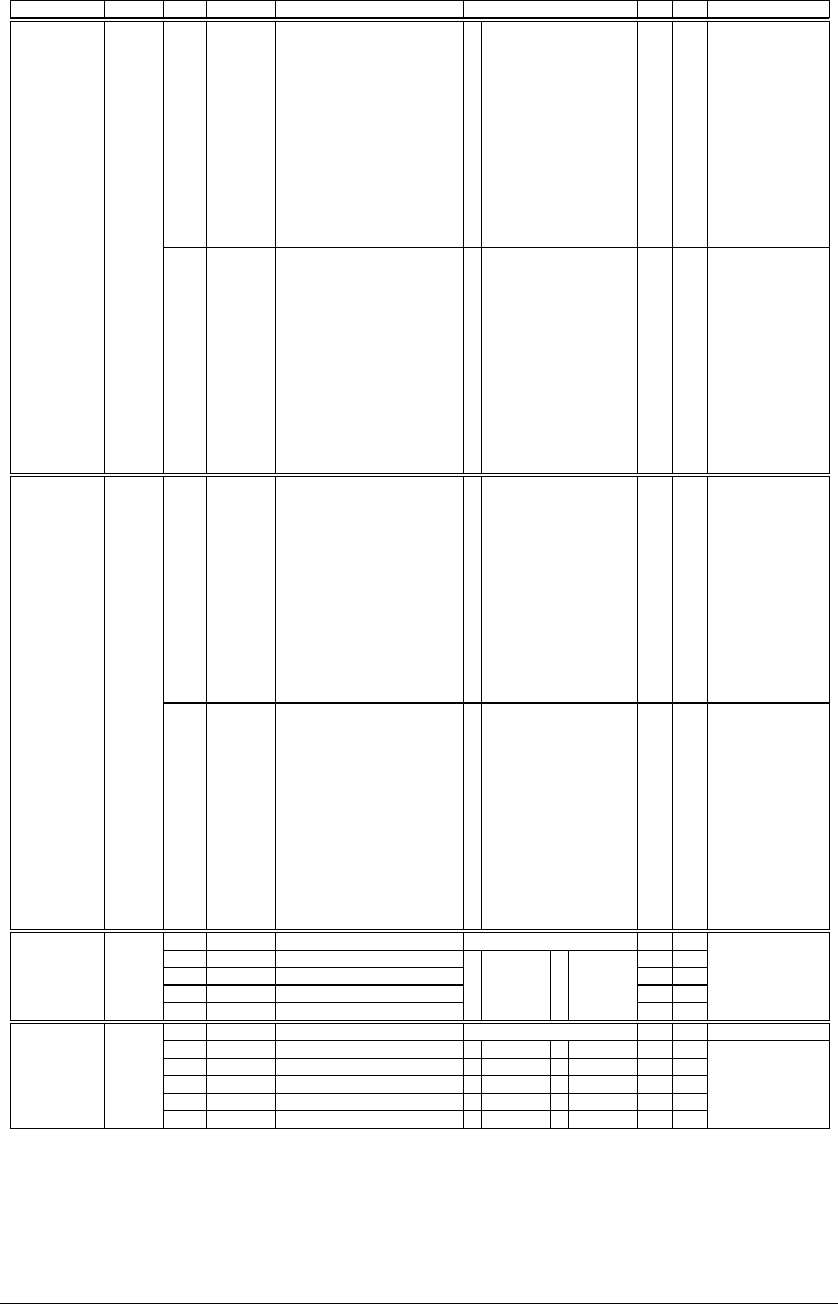

V DMA BLOCK: HSDMA (High-Speed DMA)

B-V-2-18 EPSON S1C33L03 FUNCTION PART

NameAddressRegister name Bit Function Setting Init. R/W Remarks

HSD1S3

HSD1S2

HSD1S1

HSD1S0

HSD0S3

HSD0S2

HSD0S1

HSD0S0

D7

D6

D5

D4

D3

D2

D1

D0

High-speed DMA Ch.1

trigger set-up

High-speed DMA Ch.0

trigger set-up

0

0

0

0

0

0

0

0

R/W

R/W

0040298

(B)

0

1

2

3

4

5

6

7

8

9

A

B

C

Software trigger

K51 input (falling edge)

K51 input (rising edge)

Port 1 input

Port 5 input

8-bit timer Ch.1 underflow

16-bit timer Ch.1 compare B

16-bit timer Ch.1 compare A

16-bit timer Ch.5 compare B

16-bit timer Ch.5 compare A

SI/F Ch.1 Rx buffer full

SI/F Ch.1 Tx buffer empty

A/D conversion completion

0

1

2

3

4

5

6

7

8

9

A

B

C

Software trigger

K50 input (falling edge)

K50 input (rising edge)

Port 0 input

Port 4 input

8-bit timer Ch.0 underflow

16-bit timer Ch.0 compare B

16-bit timer Ch.0 compare A

16-bit timer Ch.4 compare B

16-bit timer Ch.4 compare A

SI/F Ch.0 Rx buffer full

SI/F Ch.0 Tx buffer empty

A/D conversion completion

High-speed

DMA Ch.0/1

trigger set-up

register

HSD3S3

HSD3S2

HSD3S1

HSD3S0

HSD2S3

HSD2S2

HSD2S1

HSD2S0

D7

D6

D5

D4

D3

D2

D1

D0

High-speed DMA Ch.3

trigger set-up

High-speed DMA Ch.2

trigger set-up

0

0

0

0

0

0

0

0

R/W

R/W

0040299

(B)

0

1

2

3

4

5

6

7

8

9

A

B

C

Software trigger

K54 input (falling edge)

K54 input (rising edge)

Port 3 input

Port 7 input

8-bit timer Ch.3 underflow

16-bit timer Ch.3 compare B

16-bit timer Ch.3 compare A

16-bit timer Ch.5 compare B

16-bit timer Ch.5 compare A

SI/F Ch.1 Rx buffer full

SI/F Ch.1 Tx buffer empty

A/D conversion completion

0

1

2

3

4

5

6

7

8

9

A

B

C

Software trigger

K53 input (falling edge)

K53 input (rising edge)

Port 2 input

Port 6 input

8-bit timer Ch.2 underflow

16-bit timer Ch.2 compare B

16-bit timer Ch.2 compare A

16-bit timer Ch.4 compare B

16-bit timer Ch.4 compare A

SI/F Ch.0 Rx buffer full

SI/F Ch.0 Tx buffer empty

A/D conversion completion

High-speed

DMA Ch.2/3

trigger set-up

register

–

HST3

HST2

HST1

HST0

D7–4

D3

D2

D1

D0

reserved

HSDMA Ch.3 software trigger

HSDMA Ch.2 software trigger

HSDMA Ch.1 software trigger

HSDMA Ch.0 software trigger

–

0

0

0

0

–

W

W

W

W

0 when being read.004029A

(B)

–

1 Trigger 0 Invalid

High-speed

DMA software

trigger

register

–

CFK54

CFK53

CFK52

CFK51

CFK50

D7–5

D4

D3

D2

D1

D0

reserved

K54 function selection

K53 function selection

K52 function selection

K51 function selection

K50 function selection

– –

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.00402C0

(B)

1

#DMAREQ3

0 K54

1

#DMAREQ2

0 K53

1 #ADTRG 0 K52

1

#DMAREQ1

0 K51

1

#DMAREQ0

0 K50

K5 function

select register