II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-22 EPSON S1C33L03 FUNCTION PART

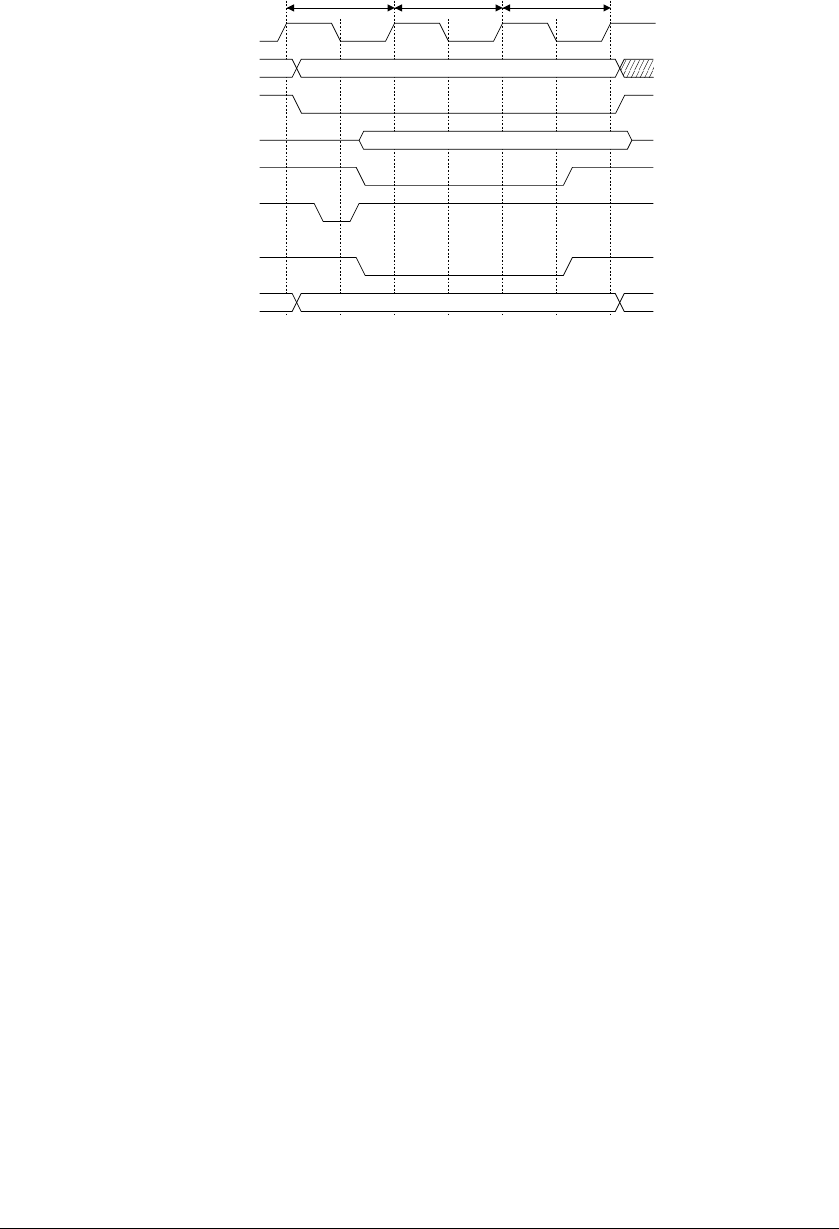

Write cycle with wait mode

Example: When the BCU has no internal wait mode, and 1 wait cycle is inserted via the #WAIT pin

BCLK

A[23:0]

#CExx

D[15:0]

#WRH/#WRL

#WAIT

#WR

#BSL/#BSH

C1 CW C2

addr

data

Figure 4.25 Half-word Write Cycle with Wait

The #WAIT signal is sampled at the falling edge of the transition of BCLK (bus clock), and the write cycle is

terminated in the cycle immediately following the cycle in which the #WAIT signal was sampled in an

inactive (high level).

Note: Insertion of wait cycles via the #WAIT pin is possible only when the device for bus conditions is set

to SRAM and SWAITE (D0) / Bus control register (0x4812E) is enabled for waiting.

The above example shows a write cycle when a wait mode is inserted via the #WAIT signal. A wait mode

consisting of 2 to 7 cycles can also be inserted using the wait control bits. The settings of these bits also can

be used in combination with the #WAIT signal. In this case as well, the #WAIT signal is sampled at the

falling edge of the transition of BCLK. However, even when the #WAIT signal is inactive before the wait

cycles set by the wait control bits are terminated, the write cycle is not terminated at that time.

Note: The basic write cycle consists of at least two cycles. This does not change regardless of whether

zero or one wait cycle is set by the wait control bits. If the number of wait cycles set is 2 or more,

the bus cycle is actually extended. In this case, the bus write cycle consists of [number of wait

cycles + 1], as in the case of read cycles (providing that there is no external wait).