IV ANALOG BLOCK: A/D CONVERTER

S1C33L03 FUNCTION PART EPSON B-IV-2-3

A-1

B-IV

A/D

Setting A/D Converter

When the A/D converter is used, the following settings must be made before an A/D conversion can be performed:

1. Setting analog input pins

2. Setting the input clock

3. Selecting the analog-conversion start and end channels

4. Setting the A/D conversion mode

5. Selecting a trigger

6. Setting the sampling time

7. Setting interrupt/IDMA/HSDMA

The following describes how to set each item. For details on how to set the analog input pins, refer to the preceding

section. For details on how to set interrupt/DMA, refer to "A/D Converter Interrupt and DMA".

Note: Before making these settings, make sure the A/D converter is disabled (ADE (D2) / A/D enable

register (0x40244) = "0"). Changing the settings while the A/D converter is enabled could cause a

malfunction.

Setting the input clock

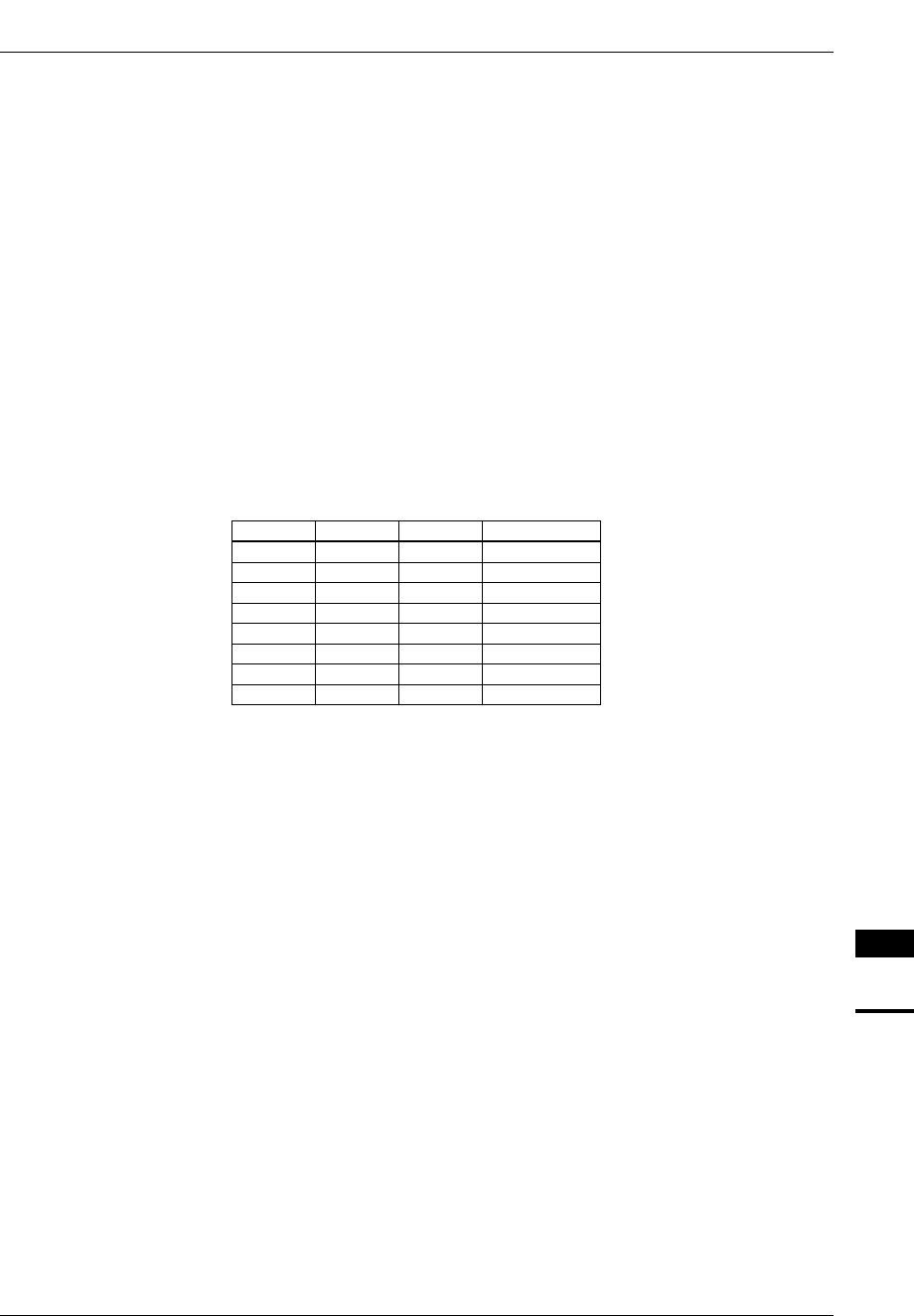

As explained in "Prescaler", the A/D conversion clock can be selected from among the eight types shown in

Table 2.2 below. Use PSAD[2:0] (D[2:0]) / A/D clock control register (0x4014F) for this selection.

Table 2.2 Input Clock Selection

PSAD2 PSAD1 PSAD0 Division ratio

111fPSCIN/256

110fPSCIN/128

101fPSCIN/64

100fPSCIN/32

011fPSCIN/16

010fPSCIN/8

001fPSCIN/4

000fPSCIN/2

fPSCIN: Prescaler input clock frequency

The selected clock is output from the prescaler to the A/D converter by writing "1" to PSONAD (D3) / A/D

clock control register (0x4014F).

Notes:•The A/D converter operates only when the prescaler is operating.

•The recommended input clock frequency is a maximum of 2 MHz.

•Do not start an A/D conversion when the clock output from the prescaler to the A/D converter is

turned off, and do not turn off the prescaler's clock output when an A/D conversion is underway.

This could cause the A/D converter to operate erratically.

Selecting analog-conversion start and end channels

Select the channel in which the A/D conversion is to be performed from among the pins (channels) that have

been set for analog input. To enable A/D conversions in multiple channels to be performed successively

through one convert operation, specify the conversion start and conversion end channels.

Conversion start channel: CS[2:0] (D[2:0]) / A/D channel register (0x40243)

Conversion end channel: CE[2:0] (D[5:3]) / A/D channel register (0x40243)