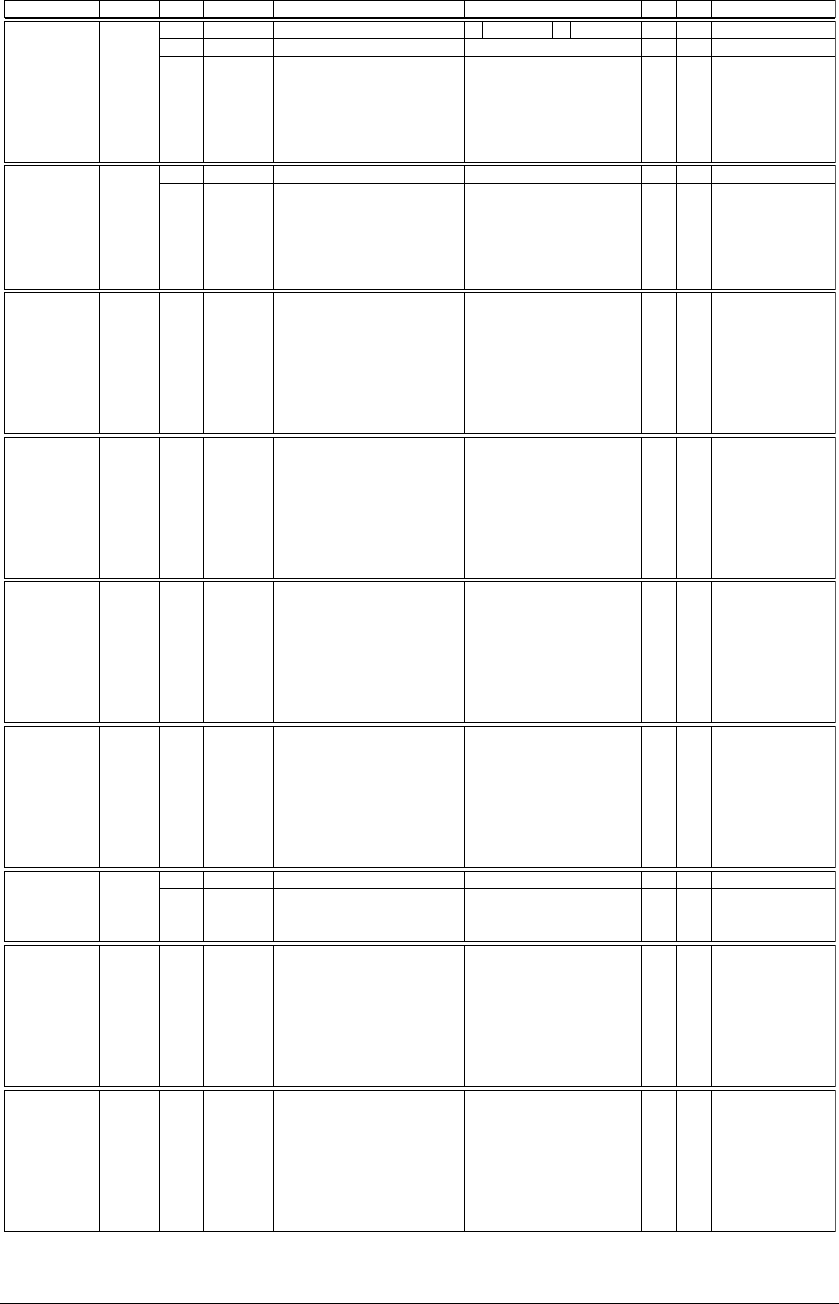

VII LCD CONTROLLER BLOCK: LCD CONTROLLER

B-VII-2-32 EPSON S1C33L03 FUNCTION PART

NameAddressRegister name Bit Function Setting Init. R/W Remarks

VNDPF

–

VNDP5

VNDP4

VNDP3

VNDP2

VNDP1

VNDP0

D7

D6

D5

D4

D3

D2

D1

D0

Vertical non-display period status

reserved

Vertical non-display period

0

–

0

0

0

0

0

0

R

–

R/W

0 when being read.

039FFEA

(B)

Vertical

non-display

period register

–

Non display period (lines)

1 VNDP 0 Display

–

MODRATE5

MODRATE4

MODRATE3

MODRATE2

MODRATE1

MODRATE0

D7–6

D5

D4

D3

D2

D1

D0

reserved

MOD rate

–

0

0

0

0

0

0

–

R/W

0 when being read.039FFEB

(B)

MOD rate

register

–

S1ADDR7

S1ADDR6

S1ADDR5

S1ADDR4

S1ADDR3

S1ADDR2

S1ADDR1

S1ADDR0

D7

D6

D5

D4

D3

D2

D1

D0

Screen 1 start address

(low-order 8 bits)

0

0

0

0

0

0

0

0

R/W039FFEC

(B)

Screen 1

start address

register 0

S1ADDR15

S1ADDR14

S1ADDR13

S1ADDR12

S1ADDR11

S1ADDR10

S1ADDR9

S1ADDR8

D7

D6

D5

D4

D3

D2

D1

D0

Screen 1 start address

(high-order 8 bits)

0

0

0

0

0

0

0

0

R/W039FFED

(B)

Screen 1

start address

register 1

S2ADDR7

S2ADDR6

S2ADDR5

S2ADDR4

S2ADDR3

S2ADDR2

S2ADDR1

S2ADDR0

D7

D6

D5

D4

D3

D2

D1

D0

Screen 2 start address

(low-order 8 bits)

0

0

0

0

0

0

0

0

R/W039FFEE

(B)

Screen 2

start address

register 0

S2ADDR15

S2ADDR14

S2ADDR13

S2ADDR12

S2ADDR11

S2ADDR10

S2ADDR9

S2ADDR8

D7

D6

D5

D4

D3

D2

D1

D0

Screen 2 start address

(high-order 8 bits)

0

0

0

0

0

0

0

0

R/W039FFEF

(B)

Screen 2

start address

register 1

–

S1ADDR16

D7–1

D0

reserved

Screen 1 start address (MSB)

(for portrait mode;

fix at 0 in landscape mode)

–

0

–

R/W

0 when being read.039FFF0

(B)

Screen 1

start address

register 2

–

MADOFS7

MADOFS6

MADOFS5

MADOFS4

MADOFS3

MADOFS2

MADOFS1

MADOFS0

D7

D6

D5

D4

D3

D2

D1

D0

Memory address offset 0

0

0

0

0

0

0

0

R/W039FFF1

(B)

Memory

address offset

register

S1VSIZE7

S1VSIZE6

S1VSIZE5

S1VSIZE4

S1VSIZE3

S1VSIZE2

S1VSIZE1

S1VSIZE0

D7

D6

D5

D4

D3

D2

D1

D0

Screen 1 vertical size

(low-order 8 bits)

0

0

0

0

0

0

0

0

R/W039FFF2

(B)

Screen 1

vertical size

register 0