VII LCD CONTROLLER BLOCK: LCD CONTROLLER

B-VII-2-38 EPSON S1C33L03 FUNCTION PART

LCLKSEL[2:0]: LCDC clock select (D[2:0]) / FIFO control register (0x39FFF4)

Selects the operating clock for the LCD controller. The selected clock is used as the LCD controller’s pixel clock

PCLK and display memory clock MCLK. The maximum clock frequency that can be supplied to the LCD

controller is 25 MHz.

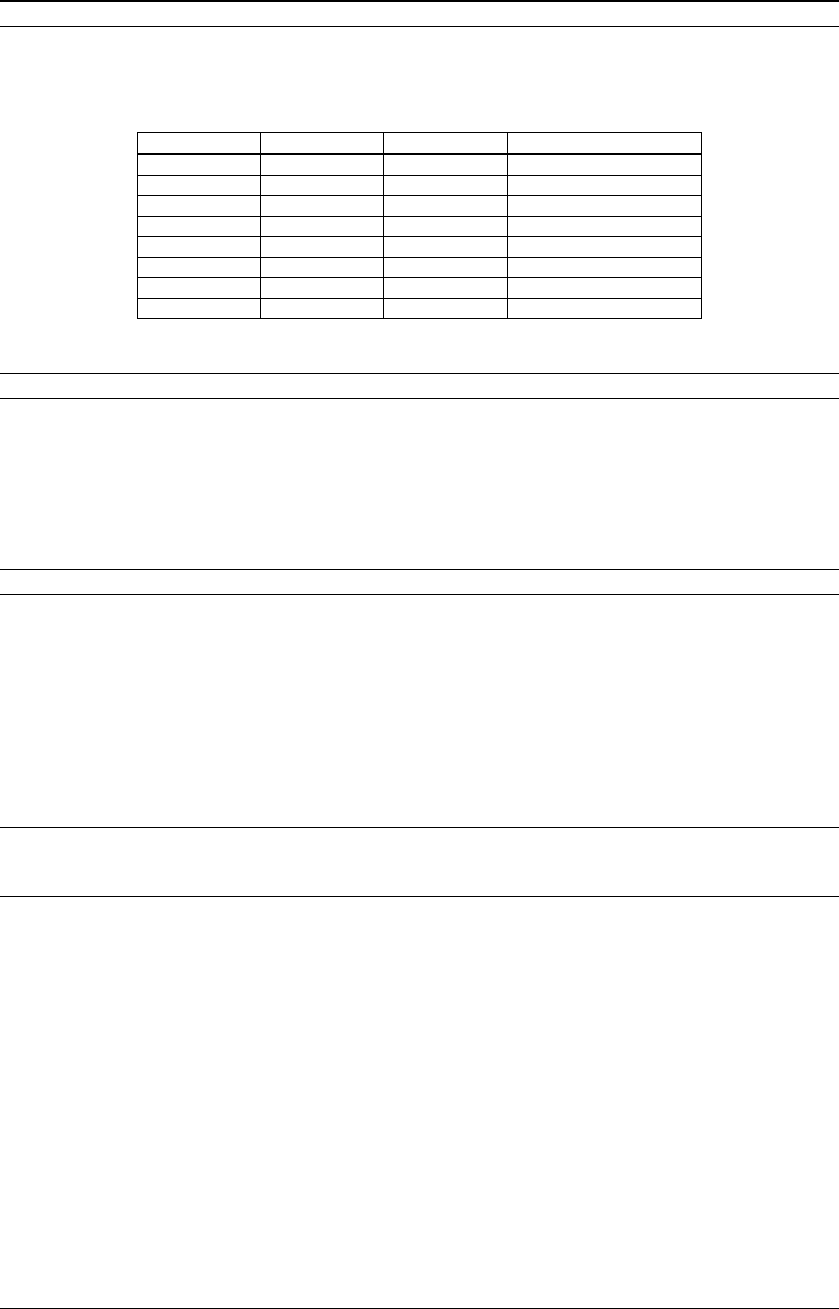

Table 2.25 Selection of LCDC Clocks

LCLKSEL2 LCLKSEL1 LCLKSEL0 LCDC clock

000Turned off

001Turned off

010Turned off

011Reserved (not allowed)

100BCU_CLK

101BCU_CLK/2

110BCU_CLK/3

111BCU_CLK/4

At initial reset, LCLKSEL is set to "0x0" (clock turned off).

LUTADDR[3:0]: LUT address (D[3:0]) / Look-up table address register (0x39FFF5)

Specifies the initial address (entry) of the look-up table in which to write data. Writing data (0–15) to this register

selects an entry (0–15) in the red look-up table. When data is set in the look-up-table data registers in order of red,

green, and blue, the data is written to the specified entries in the red, green, and blue look-up tables. LUTADDR is

incremented at the same time data is written, indicating the next entry. Once an entry is specified, data can be

written to the look-up tables successively. The entry address is also incremented in the same way when data is read

from the look-up-table data registers. This register must always be accessed bytewise for both reading and writing.

At initial reset, LUTADDR is set to "0x0" (entry 0 in the red look-up table).

LUTDT[3:0]: LUT data (D[7:4]) / Look-up table data register (0x39FFF7)

Use this register to read or write to the look-up tables.

Each time this register is accessed, the look-up-table pointer changes in the order shown below (provided that the

look-up-table address register is set to 0x0).

R[0]→G[0]→B[0]→(LUTADDR incremented)→R[1]→G[1]→B[1]

The data set in the look-up tables can be read out by reading this register. When read, the 4 low-order bits of the

register are set to 0x0. The data written to this register are set in the look-up tables. Note, however, that no data is

set in the look-up tables until data is written to the register three times, in order of red, green, and blue. Write 0x0

to the 4 low-order bits of the register.

At initial reset, LUTDT is set to "0x0".

GPIO2C: GPIO2 configuration (D2) / GPIO configuration register (0x39FFF8)

GPIO1C: GPIO1 configuration (D1) / GPIO configuration register (0x39FFF8)

GPIO0C: GPIO0 configuration (D0) / GPIO configuration register (0x39FFF8)

Selects the input/output modes of the GPIO[2:0] pins.

Write "1": Output mode

Write "0": Input mode

Read: Valid

Setting GPIOxC to "1" directs GPIOx for output, and setting GPIOxC to "0" directs GPIOx for input.

The GPIO[2:0] pins are shared with the bus release pins listed below. These pins can only be used as GPIO[2:0]

pins when LCDCEN (D5/0x39FFE3) = "1" and BREQEN (D2/0x39FFFD) = "0".

GPIO2: #BUSGET/P31

GPIO1: #BUSACK/P35

GPIO0: #BUSREQ/P34

At initial reset, GPIOxC is set to "0" (input mode).