II CORE BLOCK: BCU (Bus Control Unit)

S1C33L03 FUNCTION PART EPSON B-II-4-17

A-1

B-II

BCU

Bus Clock

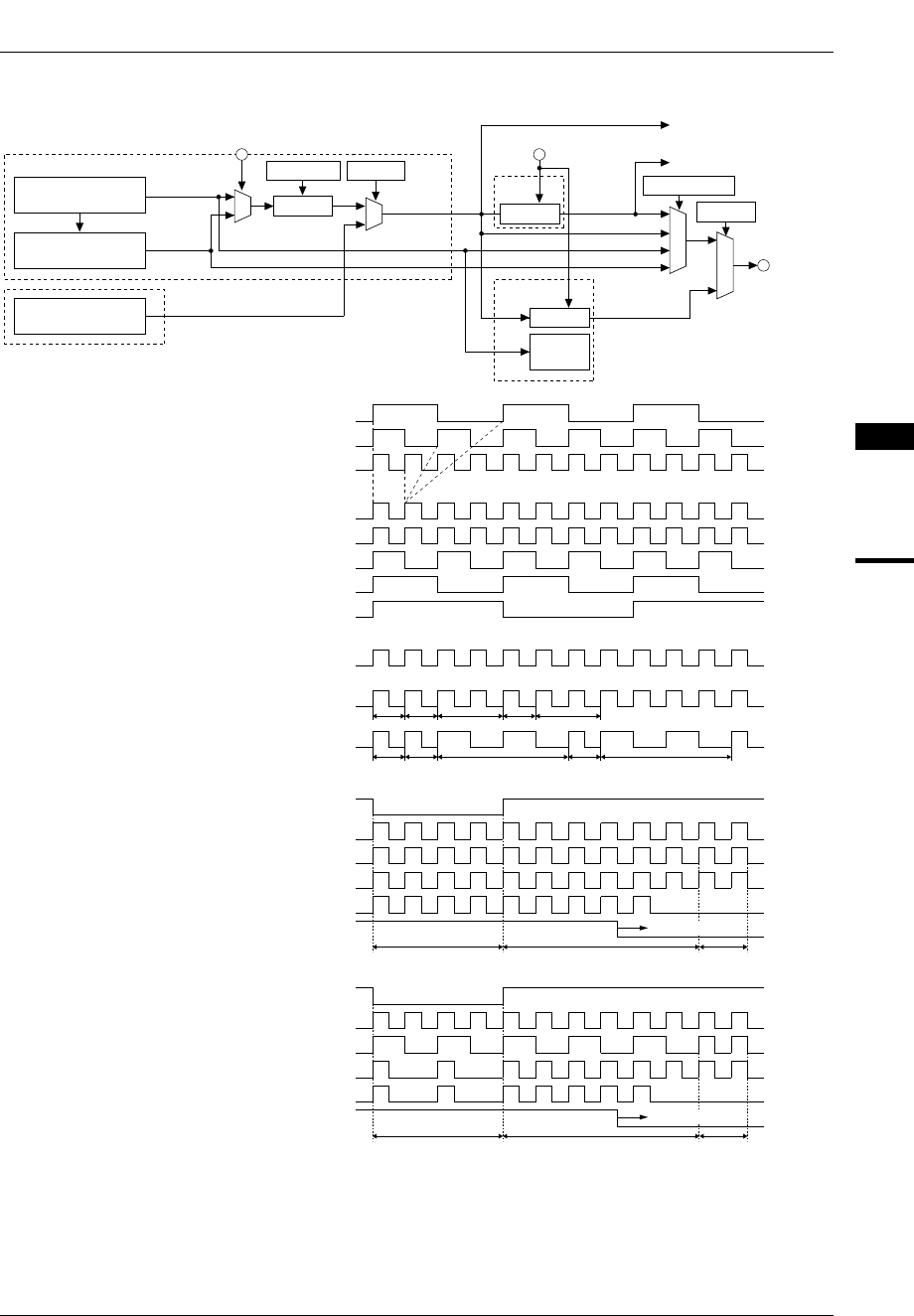

The bus clock is generated by the BCU using the CPU system clock output from the clock generator.

Figure 4.17 shows the clock system.

High-speed (OSC3)

oscillation circuit

CLKCHGCLKDT[1:0]

PLLS[1:0] pins

#X2SPD pin

To CPU

OSC3_CLK

PLL_CLK

A

CPU_CLK

BCU_CLK

CPU_CLK

OSC3_CLK

PLL_CLK

Bus clock

PLL

Low-speed (OSC1)

oscillation circuit

CLG

BCU

1/1 or 1/2

1/1–1/8

BCLKSEL[1:0]

SDRENA

SD_CLK

SDRAMC

1/1 or 1/2

Refresh

counter

BCLK pin

PLL_CLK and CPU_CLK

BCU_CLK

SD_CLK (When #X2SPD = "1")

OSC3_CLK (PLL: off)

PLL_CLK (PLL: x2 mode)

PLL_CLK (PLL: x4 mode)

A

CPU_CLK (CLKDT = 1/1)

CPU_CLK (CLKDT = 1/2)

CPU_CLK (CLKDT = 1/4)

CPU_CLK (CLKDT = 1/8)

CPU_CLK

BCU_CLK (#X2SPD = "1", x1 speed mode)

BCU_CLK (#X2SPD = "0", x2 speed mode)

(when the CPU system clock source is OSC3)

∗1

∗1 Access to the internal RAM

∗2 Access to the external memory (other than SDRAM)

∗3 Access to the SDRAM

∗1

∗1

∗1

∗2 ∗1 ∗2

∗2

∗3 ∗2 ∗1

∗1 ∗2

#SDCEx

CPU_CLK

BCU_CLK

SD_CLK (SDRCLK = "1")

SD_CLK (SDRCLK = "0")

SDCKE

Self refresh

SD_CLK (When #X2SPD = "0")

∗3 ∗2 ∗1

#SDCEx

CPU_CLK

BCU_CLK

SD_CLK (SDRCLK = "1")

SD_CLK (SDRCLK = "0")

SDCKE

Self refresh

Figure 4.17 Clock System