V DMA BLOCK: HSDMA (High-Speed DMA)

B-V-2-8 EPSON S1C33L03 FUNCTION PART

Trigger Factor

A HSDMA tigger factor can be selected from among 13 types using the HSDMA trigger set-up register for each

channel. This function is supported by the interrupt controller.

HSD0S[3:0]: Ch. 0 trigger set-up (D[3:0]) / HSDMA Ch. 0/1 trigger set-up register (0x40298)

HSD1S[3:0]: Ch. 1 trigger set-up (D[7:4]) / HSDMA Ch. 0/1 trigger set-up register (0x40298)

HSD2S[3:0]: Ch. 2 trigger set-up (D[3:0]) / HSDMA Ch. 2/3 trigger set-up register (0x40299)

HSD3S[3:0]: Ch. 3 trigger set-up (D[7:4]) / HSDMA Ch. 2/3 trigger set-up register (0x40299)

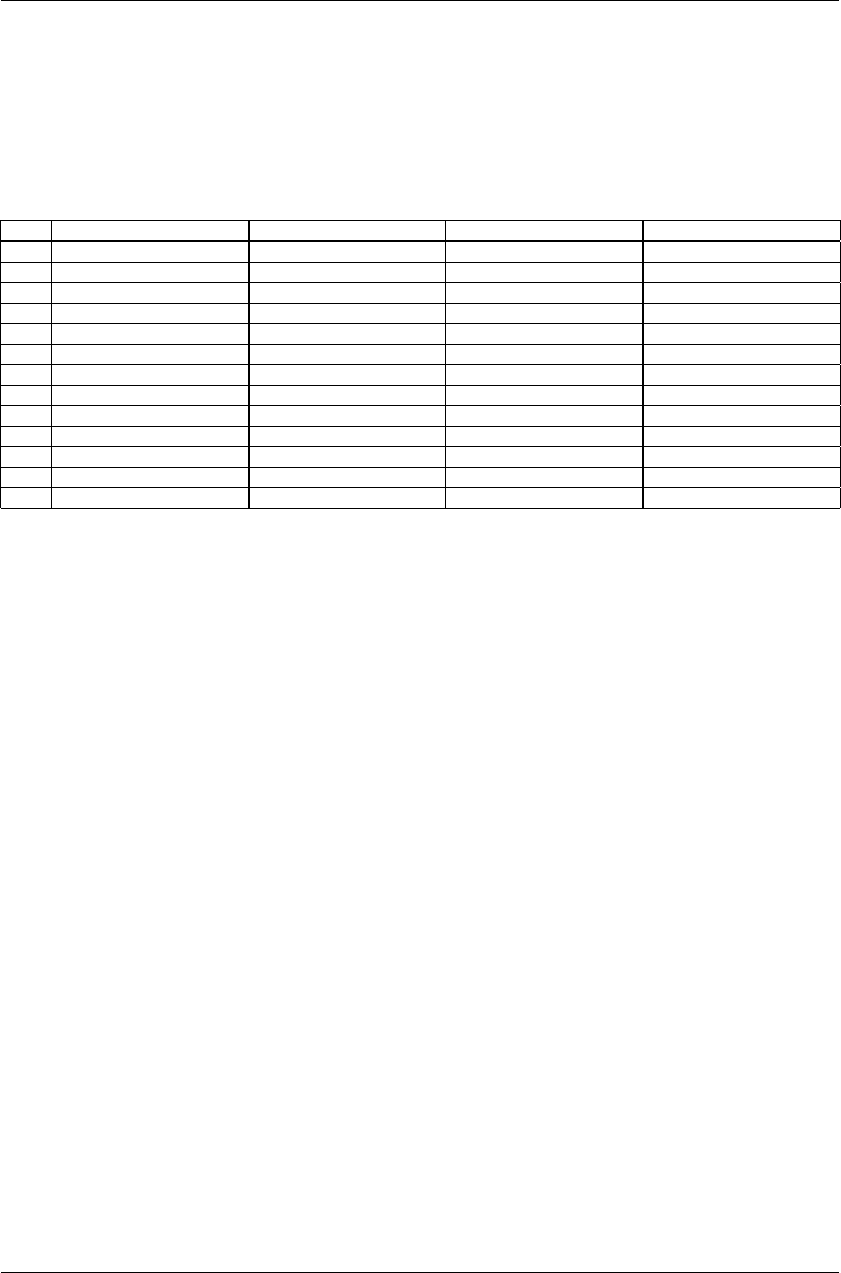

Table 2.2 shows the setting value and the corresponding trigger factor.

Table 2.2 HSDMA Trigger Factor

Value Ch.0 trigger factor Ch.1 trigger factor Ch.2 trigger factor Ch.3 trigger factor

0000 Software trigger Software trigger Software trigger Software trigger

0001 K50 port input (falling edge) K51 port input (falling edge) K53 port input (falling edge) K54 port input (falling edge)

0010 K50 port input (rising edge) K51 port input (rising edge) K53 port input (rising edge) K54 port input (rising edge)

0011 Port 0 input Port 1 input Port 2 input Port 3 input

0100 Port 4 input Port 5 input Port 6 input Port 7 input

0101 8-bit timer 0 underflow 8-bit timer 1 underflow 8-bit timer 2 underflow 8-bit timer 3 underflow

0110 16-bit timer 0 compare B 16-bit timer 1 compare B 16-bit timer 2 compare B 16-bit timer 3 compare B

0111 16-bit timer 0 compare A 16-bit timer 1 compare A 16-bit timer 2 compare A 16-bit timer 3 compare A

1000 16-bit timer 4 compare B 16-bit timer 5 compare B 16-bit timer 4 compare B 16-bit timer 5 compare B

1001 16-bit timer 4 compare A 16-bit timer 5 compare A 16-bit timer 4 compare A 16-bit timer 5 compare A

1010 Serial I/F Ch.0 Rx buffer full Serial I/F Ch.1 Rx buffer full Serial I/F Ch.0 Rx buffer full Serial I/F Ch.1 Rx buffer full

1011 Serial I/F Ch.0 Tx buffer empty Serial I/F Ch.1 Tx buffer empty Serial I/F Ch.0 Tx buffer empty Serial I/F Ch.1 Tx buffer empty

1100 A/D conversion completion A/D conversion completion A/D conversion completion A/D conversion completion

By selecting an interrupt factor with the HSDMA trigger set-up register, the HSDMA channel is invoked when the

selected interrupt factor occurs. The interrupt control bits (interrupt factor flag, interrupt enable register, IDMA

request register, interrupt priority register) do not affect this invocation. The interrupt factor that invokes HSDMA

sets the interrupt factor flag. and HSDMA does not reset the flag. Consequently, when the DMA transfer is

completed (even if the transfer counter is not 0), an interrupt request to the CPU will be generated if the interrupt

has been enabled. To generate an interrupt only when the transfer counter reaches 0, disable the interrupt by the

interrupt factor that invokes HSDMA and use the HSDMA transfer completion interrupt.

When software trigger is selected, the HSDMA channel can be invoked by writing "1" to the HSTx bit.

HST0: Ch. 0 software trigger (D0) / HSDMA software trigger register (0x4029A)

HST1: Ch. 1 software trigger (D1) / HSDMA software trigger register (0x4029A)

HST2: Ch. 2 software trigger (D2) / HSDMA software trigger register (0x4029A)

HST3: Ch. 3 software trigger (D3) / HSDMA software trigger register (0x4029A)

When the selected trigger factor occurs, the trigger flag is set to "1" to invoke the HSDMA channel.

The HSDMA starts a DMA transfer if it has been enabled and the trigger flag is cleared by the hardware at the

same time. This makes it possible to queue the HSDMA triggers that have been generated.

The trigger flag can be read and cleared using the HSx_TF bit.

HS0_TF: Ch. 0 trigger flag status/clear (D0) / Ch. 0 trigger flag register (0x4822E)

HS1_TF: Ch. 1 trigger flag status/clear (D0) / Ch. 1 trigger flag register (0x4823E)

HS2_TF: Ch. 2 trigger flag status/clear (D0) / Ch. 2 trigger flag register (0x4824E)

HS3_TF: Ch. 3 trigger flag status/clear (D0) / Ch. 3 trigger flag register (0x4825E)

By writing "1" to this bit, the set trigger flag can be cleared if the DMA transfer has not been started.

When this bit is read, "1" indicates that the flag is set and "0" indicates that the flag is cleared.