VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-14 EPSON S1C33L03 FUNCTION PART

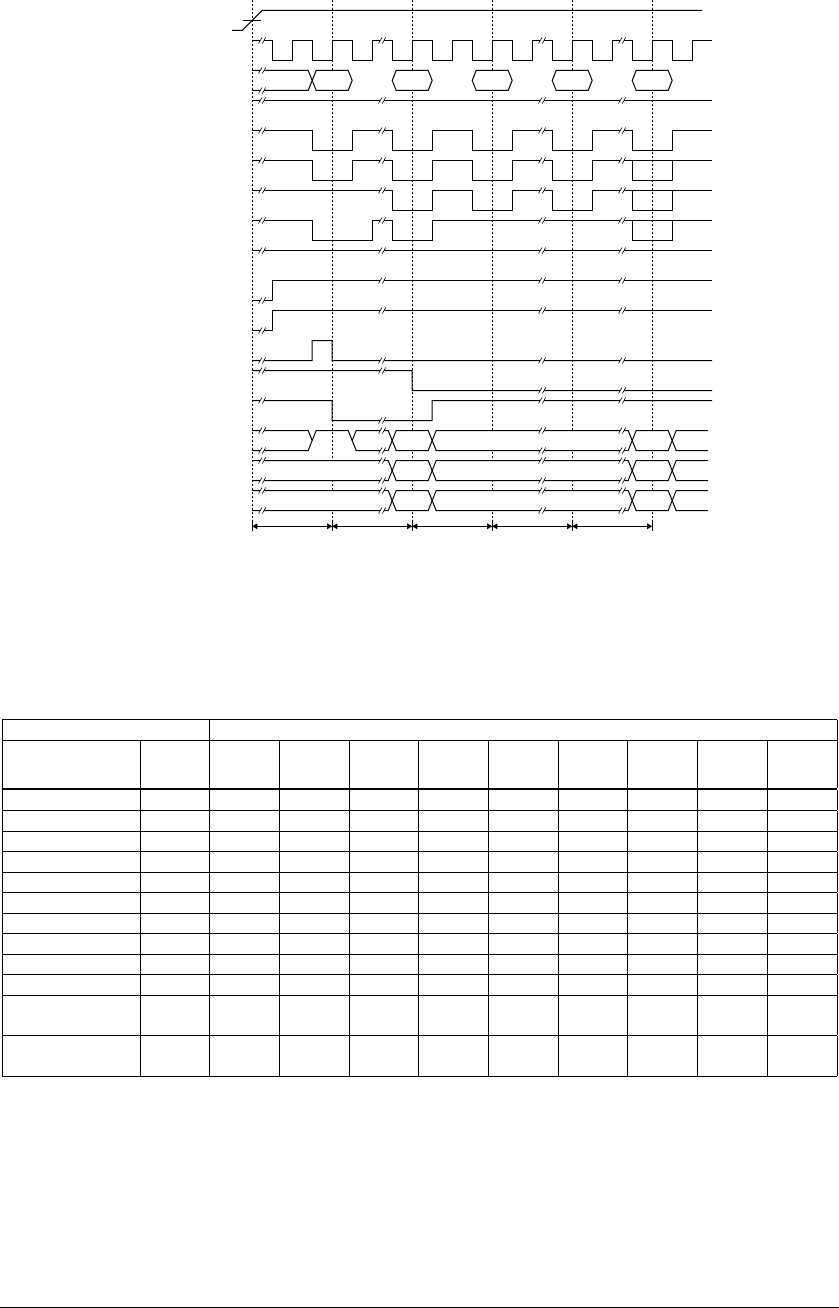

SDRAM power

BCLK

Command

SDCKE

#SDCEx

#SDRAS

#SDCAS

#SDWE

HDQM/LDQM

SDRENA bit

SDRIS bit

SDRINI bit

SDRMRS bit

Internal #WAIT

SDA10

SDBA[1:0]

SDA[12:11, 9:0]

PALLNOP

H

H

MRS REF REF CMD

Valid

Valid

Valid

Valid

Valid

Valid

100 µs min. t

RP

t

RSC

t

RC

t

RC

V

CC(Min.)

Figure 2.10 SDRAM Power-up and Initialization

SDRAM Commands

The SDRAM is controlled by commands that are comprised of a combination of high or low logic level signals.

Table 2.11 lists the commands output by the SDRAM controller.

Table 2.11 List of the Supported SDRAM Commands

Command Pins

Function

Symbol SDCKE

DQM

H/LDQM

Bank

A[15:14]

SDA10

SDA

A[13:12]

A[10:1]

#SDCEx #SDRAS #SDCAS #SDWE

Bank Active ACTV H X V V V L L H H

Bank Precharge PRE H X V L X L L H L

Precharge All PALL H X X H X L L H L

Write WRIT H XVLVLHLL

Read READ H XVLVLHLH

Mode Register Set MRS H X V V V LLLL

Deselect / NOP NOP HXXXXHXXX

Auto Refresh REF H X X X X L L L H

Self Refresh Entry SELF H → LX XXXLLLH

Self Refresh Exit – L → HX XXXHXXX

Data Write/Output

Enable

–HLXXXXXXX

Data Write/Output

Disable

–HHXXXXXXX

V = valid, X = don’t care, L = low level, H = high level

Because all of these commands are output by the SDRAM controller as necessary, they do not need to be

controlled by a user program, except for the commencement of initialization by SDRINI.