8 ELECTRICAL CHARACTERISTICS

S1C33L03 PRODUCT PART EPSON A-85

A-1

A-8

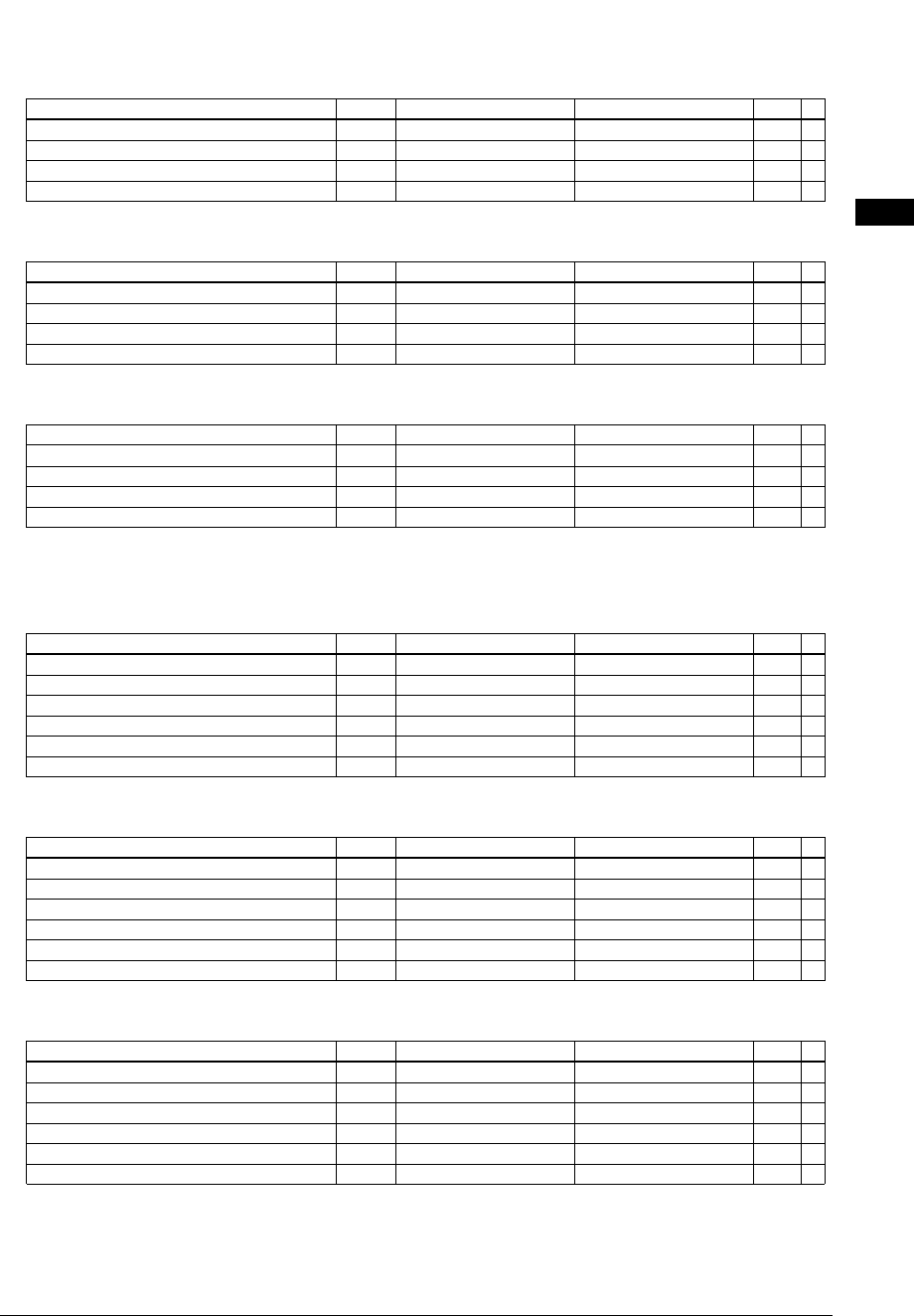

Burst ROM read cycle

1) 3.3 V/5.0 V dual power source

(Unless otherwise specified: VDDE=5.0V±0.5V, VDD=2.7V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

Read address access time (2) tACC2 tCYC(1+WC)-20 ns

Chip enable access time (2) tCEAC2 tCYC(1+WC)-20 ns

Read signal access time (2) tRDAC2 tCYC(0.5+WC)-20 ns

Burst address access time tACCB tCYC(1+WC)-20 ns

2) 3.3 V single power source

(Unless otherwise specified: VDDE=VDD=2.7V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

Read address access time (2) tACC2 tCYC(1+WC)-25 ns

Chip enable access time (2) tCEAC2 tCYC(1+WC)-25 ns

Read signal access time (2) tRDAC2 tCYC(0.5+WC)-25 ns

Burst address access time tACCB tCYC(1+WC)-25 ns

3) 2.0 V single power source

(Unless otherwise specified: VDDE=VDD=2.0V±0.2V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

Read address access time (2) tACC2 tCYC(1+WC)-60 ns

Chip enable access time (2) tCEAC2 tCYC(1+WC)-60 ns

Read signal access time (2) tRDAC2 tCYC(0.5+WC)-60 ns

Burst address access time tACCB tCYC(1+WC)-60 ns

External bus master and NMI

1) 3.3 V/5.0 V dual power source

(Unless otherwise specified: VDDE=5.0V±0.5V, VDD=2.7V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

#BUSREQ signal setup time tBRQS 15 ns

#BUSREQ signal hold time tBRQH 0ns

#BUSACK signal output delay time tBAKD 10 ns

High-impedance → output delay time tZ2E 10 ns

Output → high-impedance delay time tB2Z 10 ns

#NMI pulse width tNMIW 30 ns

2) 3.3 V single power source

(Unless otherwise specified: VDDE=VDD=2.7V to 3.6V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

#BUSREQ signal setup time tBRQS 15 ns

#BUSREQ signal hold time tBRQH 0ns

#BUSACK signal output delay time tBAKD 10 ns

High-impedance → output delay time tZ2E 10 ns

Output → high-impedance delay time tB2Z 10 ns

#NMI pulse width tNMIW 30 ns

3) 2.0 V single power source

(Unless otherwise specified: VDDE=VDD=2.0V±0.2V, VSS=0V, Ta=-40°C to +85°C)

Item Symbol Min. Max. Unit ∗

#BUSREQ signal setup time tBRQS 40 ns

#BUSREQ signal hold time tBRQH 0ns

#BUSACK signal output delay time tBAKD 20 ns

High-impedance → output delay time tZ2E 20 ns

Output → high-impedance delay time tB2Z 20 ns

#NMI pulse width tNMIW 90 ns