IV ANALOG BLOCK: A/D CONVERTER

B-IV-2-10 EPSON S1C33L03 FUNCTION PART

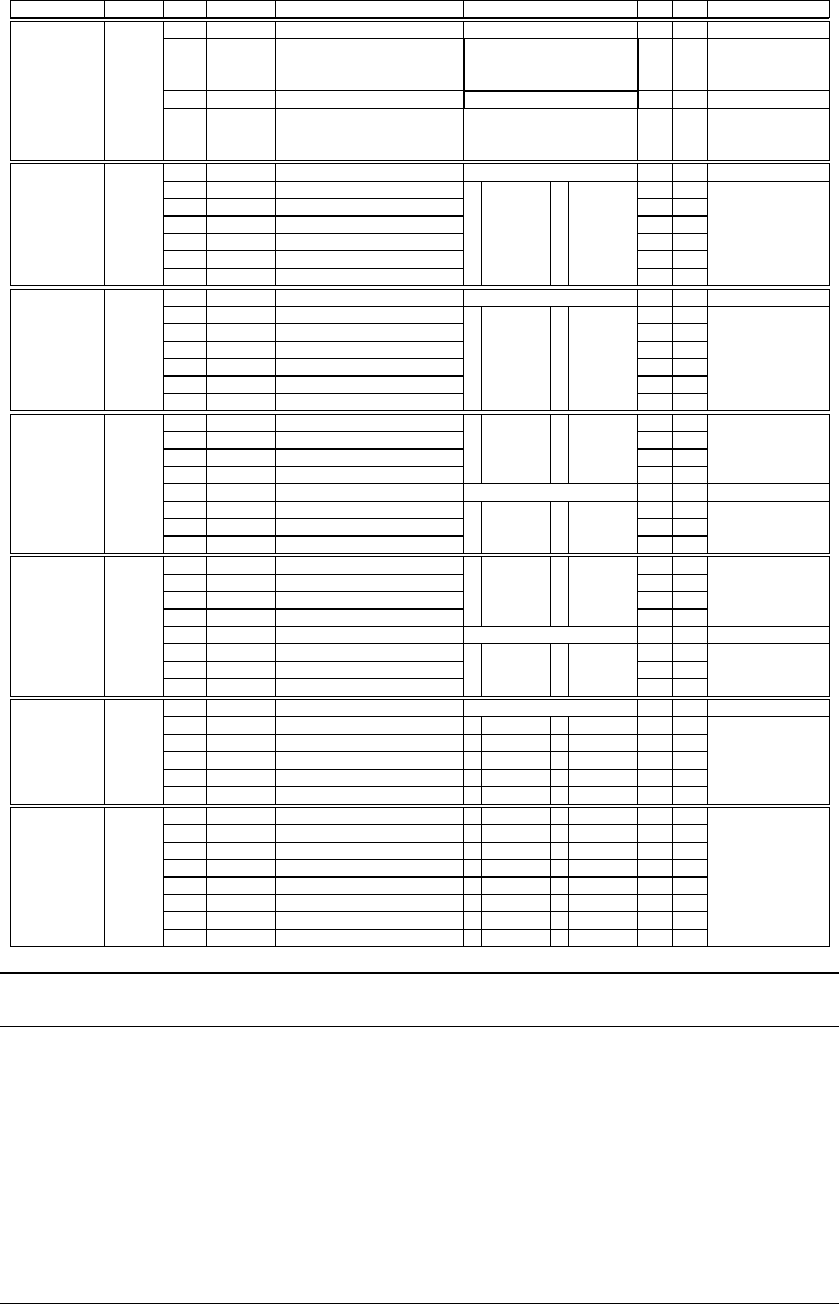

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

0 to 7

0 to 7

–

–

PAD2

PAD1

PAD0

–

PSIO12

PSIO11

PSIO10

D7

D6

D5

D4

D3

D2

D1

D0

reserved

A/D converter interrupt level

reserved

Serial interface Ch.1

interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026A

(B)

Serial I/F Ch.1,

A/D interrupt

priority register

–

EP7

EP6

EP5

EP4

ECTM

EADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040277

(B)

1 Enabled 0 Disabled

Port input 4–7,

clock timer,

A/D interrupt

enable register

–

FP7

FP6

FP5

FP4

FCTM

FADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

– –

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040287

(B)

1 Factor is

generated

0 No factor is

generated

Port input 4–7,

clock timer, A/D

interrupt factor

flag register

RP7

RP6

RP5

RP4

–

RADE

RSTX1

RSRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040293

(B)

1 IDMA

request

0 Interrupt

request

1 IDMA

request

0 Interrupt

request

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA request

register

DEP7

DEP6

DEP5

DEP4

–

DEADE

DESTX1

DESRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040297

(B)

1 IDMA

enabled

0 IDMA

disabled

1 IDMA

enabled

0 IDMA

disabled

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA enable

register

–

CFK54

CFK53

CFK52

CFK51

CFK50

D7–5

D4

D3

D2

D1

D0

reserved

K54 function selection

K53 function selection

K52 function selection

K51 function selection

K50 function selection

– –

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.00402C0

(B)

1

#DMAREQ3

0 K54

1

#DMAREQ2

0 K53

1 #ADTRG 0 K52

1

#DMAREQ1

0 K51

1

#DMAREQ0

0 K50

K5 function

select register

CFK67

CFK66

CFK65

CFK64

CFK63

CFK62

CFK61

CFK60

D7

D6

D5

D4

D3

D2

D1

D0

K67 function selection

K66 function selection

K65 function selection

K64 function selection

K63 function selection

K62 function selection

K61 function selection

K60 function selection

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402C3

(B)

1 AD7 0 K67

1 AD6 0 K66

1 AD5 0 K65

1 AD4 0 K64

1 AD3 0 K63

1 AD2 0 K62

1 AD1 0 K61

1 AD0 0 K60

K6 function

select register

CFK52: K52 pin function selection (D2) / K5 function select register (0x402C0)

CFK67–CFK60: K6[7:0] pin function selection (D[7:0]) / K6 function select register (0x402C3)

Selects the pins used by the A/D converter.

Write "1": A/D converter

Write "0": Input port

Read: Valid

When an external trigger is used, write "1" to CFK52 to set the K52 pin for external trigger input #ADTRG. Select

the pin used for analog input from among K60 (AD0) through K67 (AD7) by writing "1" to CFK60 through

CFK67.

If the function select bit for a pin is set to "0", the pin is set for an input port.

At cold start, CFK is set to "0" (input port). At hot start, CFK retains its state from prior to the initial reset.