II CORE BLOCK: BCU (Bus Control Unit)

S1C33L03 FUNCTION PART EPSON B-II-4-11

A-1

B-II

BCU

Setting SRAM Timing Conditions

The areas set for the SRAM allow wait cycles and output disable delay time to be set.

Number of wait cycles: 0 to 7 (incremented in units of one cycle)

Output disable delay time: 0.5, 1.5, 2.5, 3.5 cycles

This selection can be made once every two areas except for area 6.

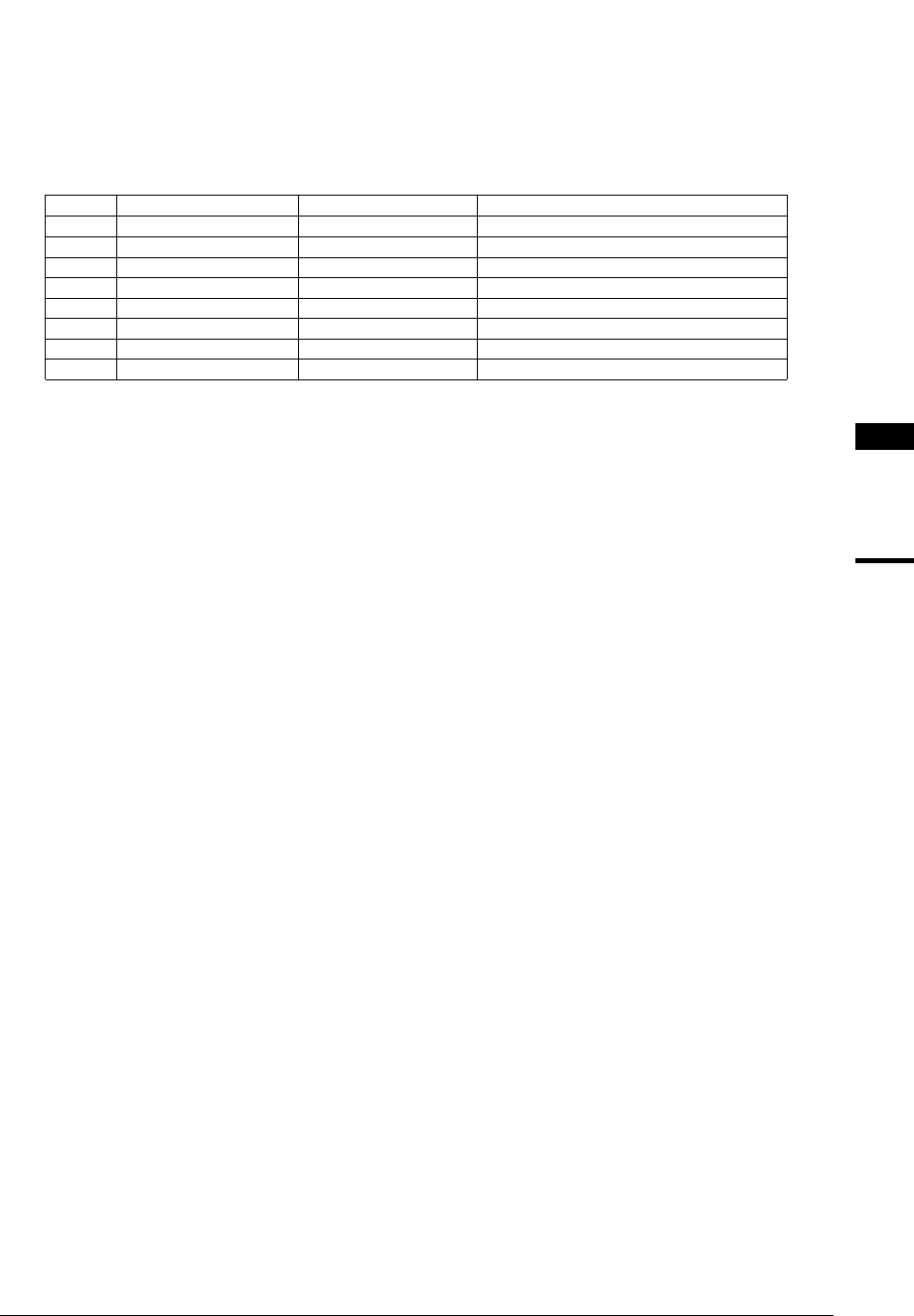

Table 4.11 Timing Condition Setting Bits (for SRAM type)

Area Number of wait cycles Output disable delay time Control register

18, 17 A18WT[2:0](D[A:8]) A18DF[1:0](D[D:C]) Areas 18–15 set-up register(0x48120)

16, 15 A16WT[2:0](D[2:0]) A16DF[1:0](D[5:4]) Areas 18–15 set-up register(0x48120)

14, 13 A14WT[2:0](D[2:0]) A14DF[1:0](D[5:4]) Areas 14–13 set-up register(0x48122)

12, 11 A12WT[2:0](D[2:0]) A12DF[1:0](D[5:4]) Areas 12–11 set-up register(0x48124)

10, 9 A10WT[2:0](D[2:0]) A10DF[1:0](D[5:4]) Areas 10–9 set-up register(0x48126)

8, 7 A8WT[2:0](D[2:0]) A8DF[1:0](D[5:4]) Areas 8–7 set-up register(0x48128)

6A6WT[2:0](D[A:8]) A6DF[1:0](D[D:C]) Areas 6–4 set-up register(0x4812A)

5, 4 A5WT[2:0](D[2:0]) A5DF[1:0](D[5:4]) Areas 6–4 set-up register(0x4812A)

At cold start, the number of wait cycles is set to 7 and the output disable delay time is set to 3.5 cycles. Reset up

these parameters as necessary using software according to specifications of the connected device.

At hot start, these parameters retain their previous settings before a reset.

Wait cycles

When the number of wait cycles is set for an area using the control bit, the BCU extends the bus cycle for a

duration equivalent to the wait cycles set when it accesses the area. Set the desired wait cycles according to

the bus clock frequency and the external device's access time. Separately from the wait cycles set here, a wait

request from an external device can also be accepted using the #WAIT pin. Since the settings of wait cycles

using software are made once every two areas, use this external wait request function if you want the wait

cycles to be controlled individually in each area or if you need 7 or more wait cycles. The #WAIT pin is

shared with the P30 I/O port. For an external wait request to be accepted, write "1" to CFP30 (D0) / P3

function select register (0x402DC [Byte]) and write "1" (default = "0") to SWAITE (D0) / Bus control

register (0x4812E) to enable the #WAIT pin.

For timing charts for bus cycles and when wait cycles are inserted, refer to "Bus Cycles in External System

Interface".

If the number of wait cycles is set to 0 and no external wait is requested, the basic read cycle (read in byte or

half-word) for the SRAM external device consists of one cycle. If wait cycles are set, because these cycles are

added, the bus read cycle consists of [number of wait cycles + 1] (providing that there is no external wait).

On the other hand, the basic write cycle consists of at least two cycles. This does not change regardless of

whether zero or one wait cycle is set. If the number of wait cycles set is 2 or more, the bus cycle is actually

extended. In this case, the bus write cycle consists of [number of wait cycles + 1], as in the case of read cycles

(providing that there is no external wait).