APPENDIX: I/O MAP

S1C33L03 FUNCTION PART EPSON B-APPENDIX-3

A-1

B-ap

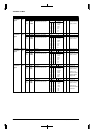

NameAddressRegister name Bit Function Setting Init. R/W Remarks

1 On 0 OffP8TON3

P8TS32

P8TS31

P8TS30

P8TON2

P8TS22

P8TS21

P8TS20

D7

D6

D5

D4

D3

D2

D1

D0

8-bit timer 3 clock control

8-bit timer 3

clock division ratio selection

8-bit timer 2 clock control

8-bit timer 2

clock division ratio selection

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

θ: selected by

Prescaler clock select

register (0x40181)

8-bit timer 3 can

generate the clock for

the serial I/F Ch.1.

θ: selected by

Prescaler clock select

register (0x40181)

8-bit timer 2 can

generate the clock for

the serial I/F Ch.0.

004014E

(B)

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P8TS3[2:0] Division ratio

θ/256

θ/128

θ/64

θ/32

θ/16

θ/8

θ/4

θ/2

1 On 0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P8TS2[2:0] Division ratio

θ/4096

θ/2048

θ/64

θ/32

θ/16

θ/8

θ/4

θ/2

8-bit timer 2/3

clock control

register

–

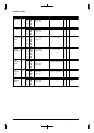

PSONAD

PSAD2

PSAD1

PSAD0

D7–4

D3

D2

D1

D0

reserved

A/D converter clock control

A/D converter clock division ratio

selection

–

0

0

0

0

–

R/W

R/W

0 when being read.

θ: selected by

Prescaler clock select

register (0x40181)

004014F

(B)

A/D clock

control register

1 On 0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P8TS0[2:0] Division ratio

θ/256

θ/128

θ/64

θ/32

θ/16

θ/8

θ/4

θ/2

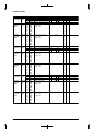

–

–

TCRST

TCRUN

D7–2

D1

D0

reserved

Clock timer reset

Clock timer Run/Stop control

–

X

X

–

W

R/W

0 when being read.

0 when being read.

0040151

(B)

1 Reset 0 Invalid

1 Run 0 Stop

–Clock timer

Run/Stop

register

TCISE2

TCISE1

TCISE0

TCASE2

TCASE1

TCASE0

TCIF

TCAF

D7

D6

D5

D4

D3

D2

D1

D0

Clock timer interrupt factor

selection

Clock timer alarm factor selection

Interrupt factor generation flag

Alarm factor generation flag

X

X

X

X

X

X

X

X

R/W

R/W

R/W

R/W

Reset by writing 1.

Reset by writing 1.

0040152

(B)

1 Generated 0

Not generated

1 Generated 0

Not generated

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

TCISE[2:0] Interrupt factor

None

Day

Hour

Minute

1 Hz

2 Hz

8 Hz

32 Hz

1

X

X

0

X

1

X

0

X

X

1

0

TCASE[2:0] Alarm factor

Day

Hour

Minute

None

Clock timer

interrupt

control register

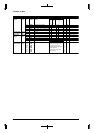

TCD7

TCD6

TCD5

TCD4

TCD3

TCD2

TCD1

TCD0

D7

D6

D5

D4

D3

D2

D1

D0

Clock timer data 1 Hz

Clock timer data 2 Hz

Clock timer data 4 Hz

Clock timer data 8 Hz

Clock timer data 16 Hz

Clock timer data 32 Hz

Clock timer data 64 Hz

Clock timer data 128 Hz

X

X

X

X

X

X

X

X

R

R

R

R

R

R

R

R

0040153

(B)

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

Clock timer

divider register

–

TCMD5

TCMD4

TCMD3

TCMD2

TCMD1

TCMD0

D7–6

D5

D4

D3

D2

D1

D0

reserved

Clock timer second counter data

TCMD5 = MSB

TCMD0 = LSB

–

X

X

X

X

X

X

–

R

0 when being read.0040154

(B)

–

0 to 59 seconds

Clock timer

second

register