III PERIPHERAL BLOCK: 8-BIT PROGRAMMABLE TIMERS

S1C33L03 FUNCTION PART EPSON B-III-3-9

A-1

B-III

8TM

High-speed DMA

The underflow interrupt factor of the timer 0 to 3 can also invoke high-speed DMA (HSDMA).

The following shows the HSDMA channel number and trigger set-up bit corresponding to the timer 0 to 3:

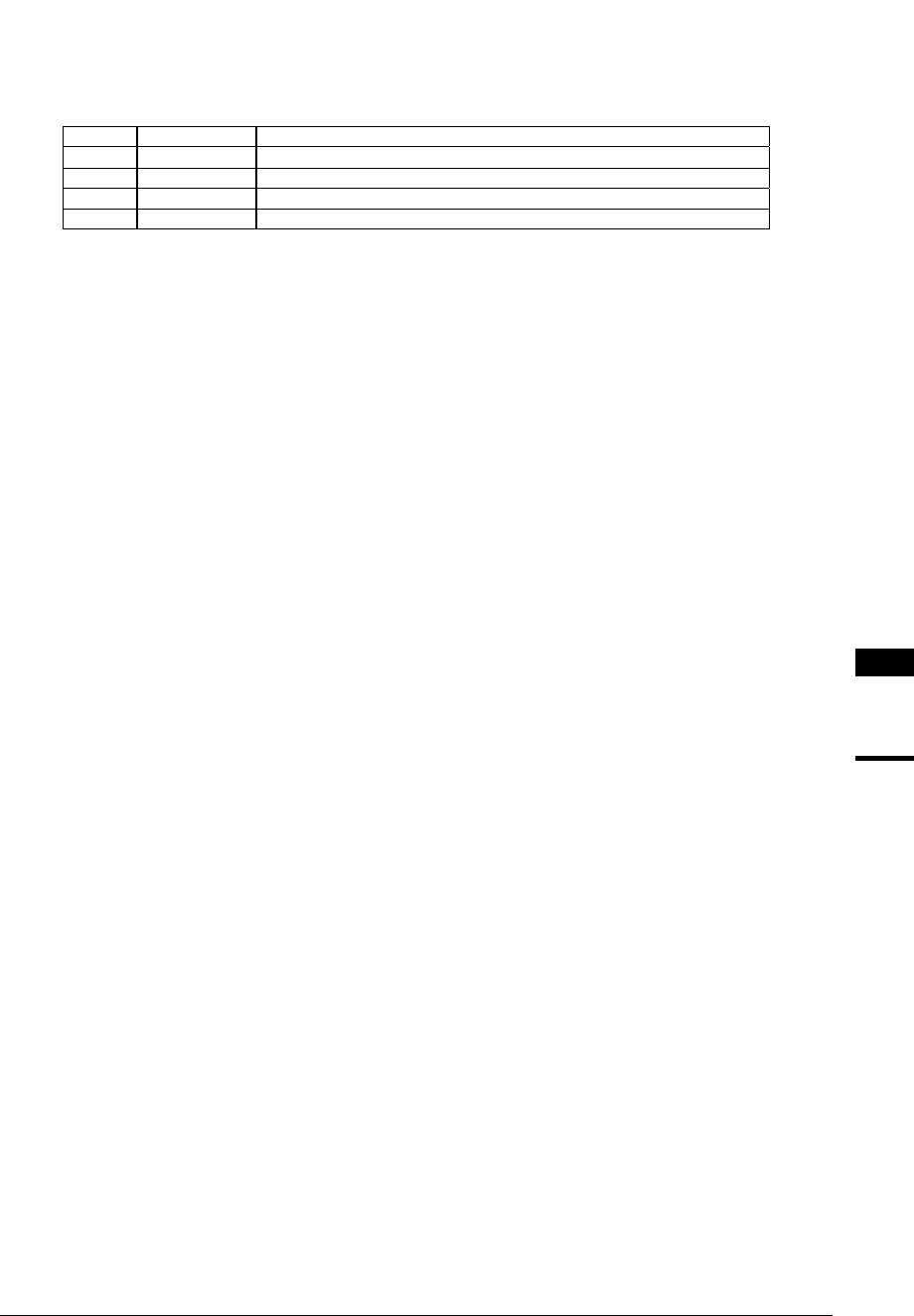

Table 3.5 HSDMA Trigger Set-up Bits

Timer HSDMA channel Trigger set-up bits

Timer 0 0 HSD0S[3:0] (D[3:0]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

Timer 1 1 HSD1S[3:0] (D[7:4]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

Timer 2 2 HSD2S[3:0] (D[3:0]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

Timer 3 3 HSD3S[3:0] (D[7:4]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

For HSDMA to be invoked, the trigger set-up bits should be set to "0101" in advance. Transfer conditions, etc.

must also be set on the HSDMA side.

If the 8-bit timer is selected as the HSDMA trigger, the HSDMA channel is invoked through generation of

the interrupt factor.

For details on HSDMA transfer, refer to "HSDMA (High-Speed DMA)".

Trap vectors

The trap vector addresses for individual underflow interrupt factors are set by default as shown below:

Timer 0 underflow interrupt: 0x0C000D0

Timer 1 underflow interrupt: 0x0C000D4

Timer 2 underflow interrupt: 0x0C000D8

Timer 3 underflow interrupt: 0x0C000DC

The base address of the trap table can be changed using the TTBR register (0x48134 to 0x48137).