8 ELECTRICAL CHARACTERISTICS

A-90 EPSON S1C33L03 PRODUCT PART

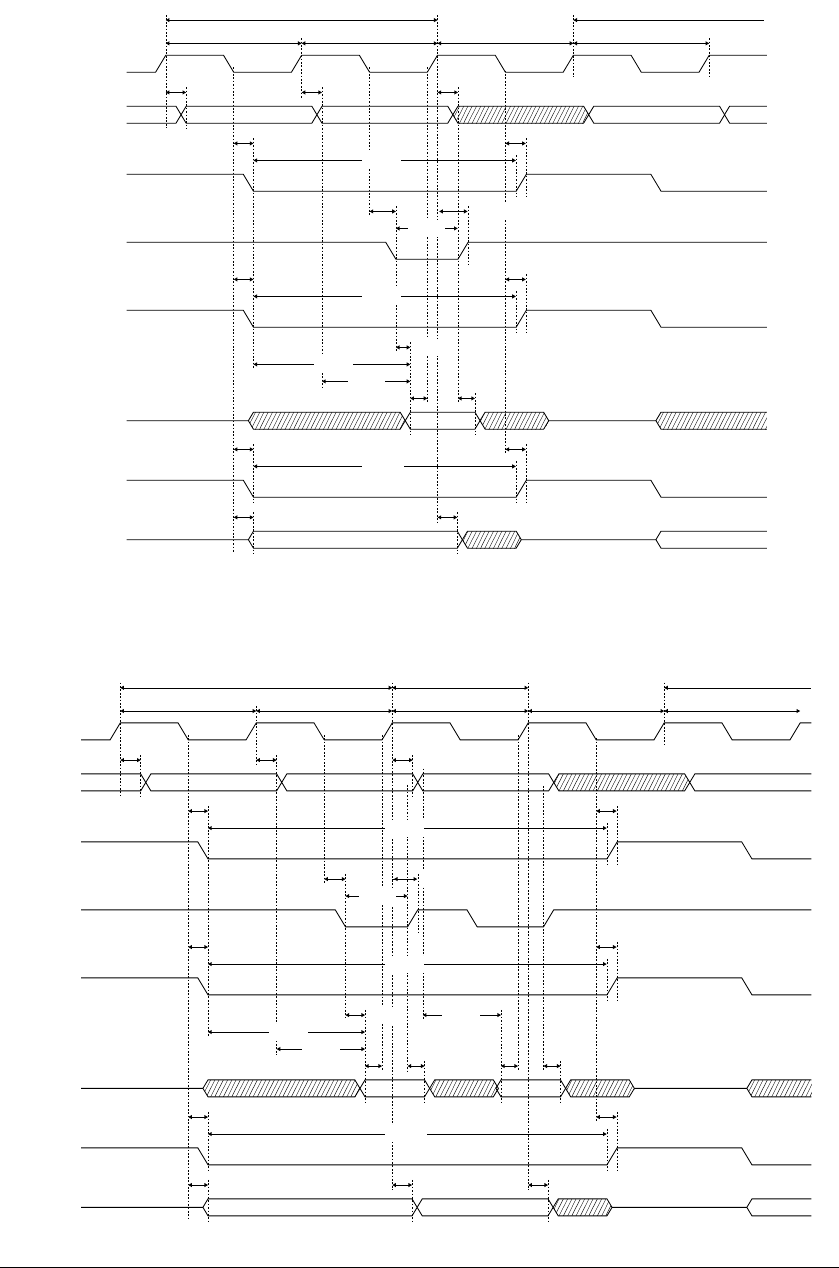

DRAM random access cycle (basic cycle)

BCLK

A[23:0]

#RAS

#HCAS/

#LCAS

#RD

D[15:0]

#WE

D[15:0]

RAS1

Data transfer #1

Next data transfer

CAS1 PRE1(precharge) RAS1' CAS1'

t

AD

t

AD

t

AD

t

CASD2

t

CASD1

t

RDS

t

ACCF

t

RACF

t

RDH

t

RASD2

t

RASD1

t

RASW

t

RDD3

t

RDD1

t

RDW2

t

WRD3

t

WRD1

t

WRW2

t

WDD1

t

WDD2

t

CASW

t

CACF

∗1

∗1 tRDH is measured with respect to the first signal change (negation) of either the #RD or the A[23:0]

signals.

DRAM fast-page access cycle

BCLK

A[23:0]

#RAS

#HCAS/

#LCAS

#RD

D[15:0]

#WE

D[15:0]

RAS1

Data transfer #1 Data transfer #2 Next data transfer

CAS1 CAS2 PRE1

(precharge)

RAS1'

t

AD

t

AD

t

AD

t

RDS

t

ACCF

t

RACF

t

RDH

t

RASD2

t

RASD1

t

RDD3

t

RDD1

t

WRD3

t

WRD1

t

WDD1

t

WDD2

t

WDD2

t

CACF

t

ACCF

t

RASW

t

RDW2

t

CASD2

t

CASD1

t

RDS

t

RDH

t

CASW

t

WRW2

∗1∗1

∗1 tRDH is measured with respect to the first signal change (negation) of either the #RD or the A[23:0] signals.